SERIES 1600 MICROPROCESSOR SYSTEM **PRICE \$8.00**

La card

GENERAL INSTRUMENT MICROELECTRONICS

# MICROCOMPUTER DOCUMENTATION

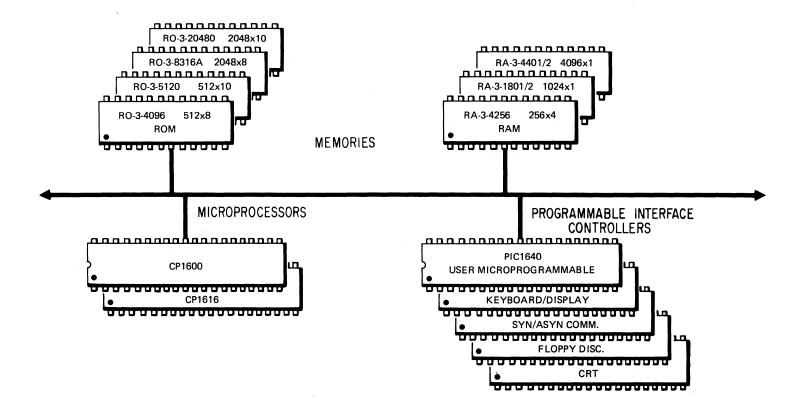

# THE SERIES 1600 SEMICONDUCTOR LINEUP

🖕 🖓 👘 👘 👘

## SERIES 1600 MICROPROCESSOR SYSTEM MICROCOMPUTER DOCUMENTATION

## GIC1600 SERIES MICROCOMPUTER USERS MANUAL MICRO MODULES DEVELOPMENT SYSTEMS RESIDENT FIRMWARE ON-LINE SOFTWARE

This manual contains a detailed description of the Series 1600 Microcomputer Modules, Prototype Development Systems and all associated hardware. Also included is a functional specification and operational information on the Resident Operating System, Debug Facilities, and On-Line Software for use on the GIC1600 Series Microcomputer Systems.

C Copyright 1975 All rights reserved

### SUMMAR Y

| Title:               | GIC1600 Series Microco                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | mputer Users Manual                   |

|----------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------|

| Document No:         | S16DOC-GIC1600-02                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | September 1975                        |

| Revision Level:      | Supersedes S16DOC-GIC                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | C1600-01 May 1975                     |

| Scope:               | This manual describes the GIC1600 series of microcomputer<br>systems including details of each module in the system. It<br>includes information on the theory of operation of the micro-<br>computer, timing of all buses and control signals, and logic<br>diagrams of all printed circuit modules. In addition, the ROM<br>Resident Operating System features are detailed along with<br>specific user operational information and command structures.<br>Lastly, all the necessary On-Line Software to make the<br>GIC1600 systems complete hardware and software development<br>tools are described along with typical examples of its use. |                                       |

| Reference Documents: | S16DOC-CP1600-04                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | CP1600 Microprocessor<br>Users Manual |

S16DOC-XALSIM-02

Series 1600 Cross Software Manual

### TABLE OF CONTENTS

| CHAF               | <b>TER 1:</b>            | GIC1600 SERIES MICROCOMPUTER SYSTEMS  | - HARDWARE |

|--------------------|--------------------------|---------------------------------------|------------|

|                    |                          |                                       | PAGE       |

| 1.0                | INTROI                   | 7                                     |            |

| 1.1                | SYSTE                    | 9                                     |            |

|                    | 1.1.1                    | System Block Diagram                  | 9          |

|                    | 1.1.2                    | Basic System Modules                  | 9          |

|                    | 1.1.3                    | System Memory Map                     | 11         |

| 1.2                | SYSTE                    | 13                                    |            |

| 1.3                | CONTR                    | OL CONSOLE OPERATION                  | 13         |

|                    | 1.3.1                    | Control Console Description           | 15         |

|                    | 1.3.2                    | Control Console Functions             | 15         |

|                    | 1.3.3                    | GIC1600 Operation via Control Console | 17         |

|                    | 1.3.4                    | Operational Flow Charts               | 17         |

| 1.4                | DATA,                    | ADDRESS & CONTROL BUSES               | 17         |

|                    | 1.4.1                    | Backplane Signal Descriptions         | 22         |

|                    | 1.4.2                    | Direct Memory Access Operation        | 33         |

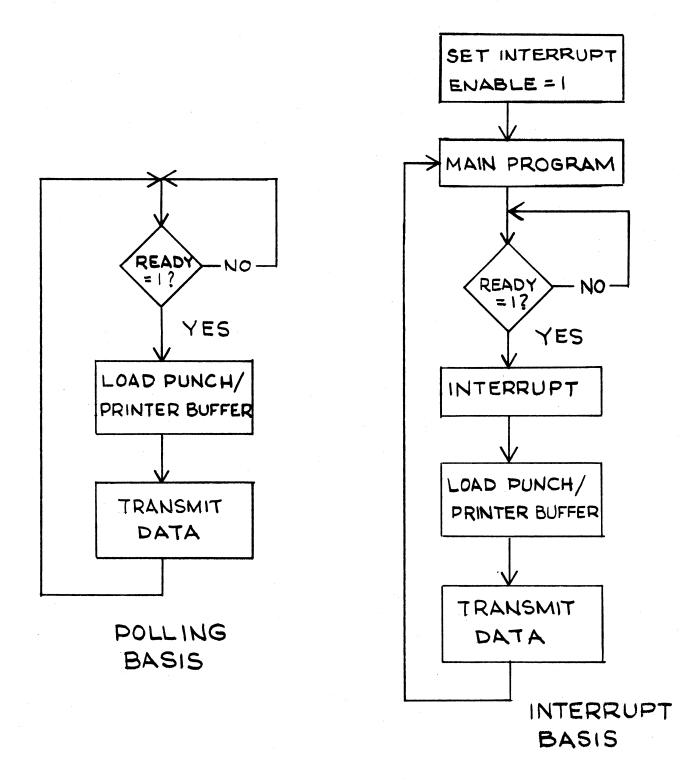

|                    | 1.4.3                    | Interrupt Operation                   | 34         |

| 1.5                | 1.5 PERIPHERAL OPERATION |                                       | 38         |

|                    | 1.5.1                    | Teletype/EIA Devices                  | 38         |

|                    | 1.5.2                    | High Speed Reader and Punch           | 41         |

| 1.6 SYSTEM MODULES |                          | M MODULES                             | 43         |

|                    | 1.6.1                    | Microcomputer Card                    | 43         |

|                    | 1.6.2                    | 2K Memory Card                        | 47         |

|                    | 1.6.3                    | 8K Memory Card                        | 49         |

|                    | 1.6.4                    | Control Console Card                  | 51         |

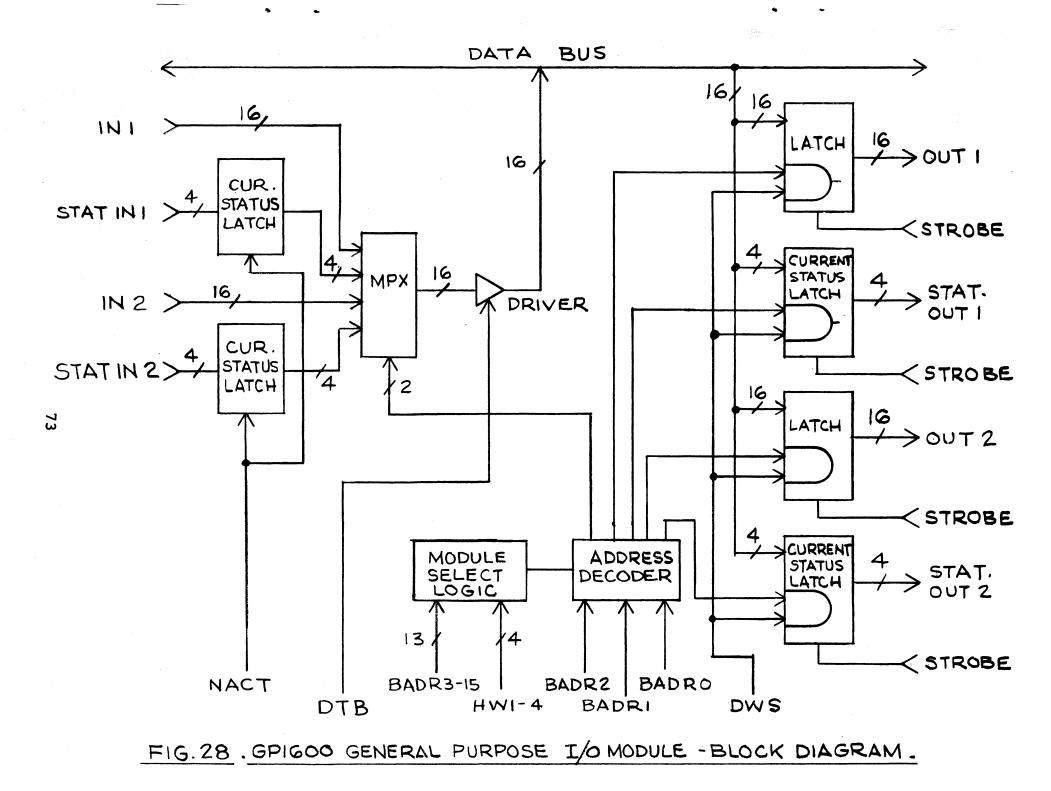

|                    | 1.6.5                    | Input/Output Card                     | 58         |

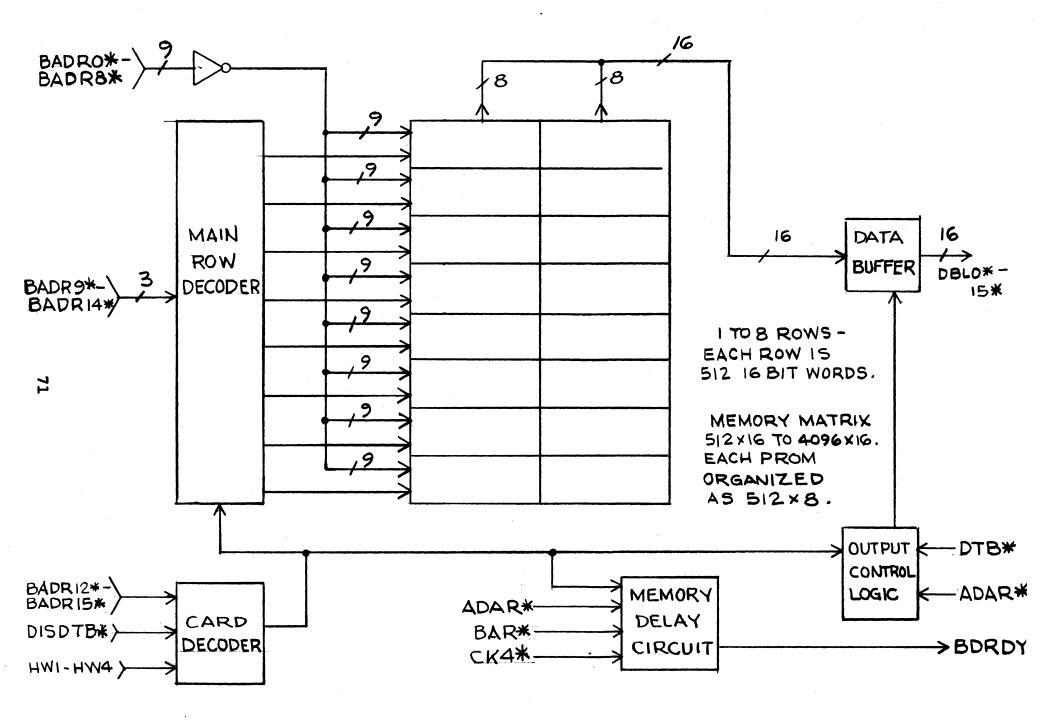

|                    | 1.6.6                    | 4K PROM Card                          | 72         |

|                    | 1.6.7                    | General Purpose Interfacing Card      | 72         |

## TABLE OF CONTENTS

| CHAP  | <b>TER 2:</b> | G    | C1600 MICROCOMPUTER SYSTEM - SOFTWARE |            |

|-------|---------------|------|---------------------------------------|------------|

| s i s |               |      |                                       | PAGE       |

| 2.0   |               |      |                                       | 74         |

| 2.1   |               |      | FIRMWARE                              | 74         |

|       | 2.1.1         |      | MTR Monitor                           | 74         |

|       | 2.1.2         |      | ODP On-Line Debug Program             | 75         |

|       | 2.1.3         |      | LDR Relocating Loader                 | 78         |

|       |               |      | DMP Memory Dump                       | 79         |

|       |               |      | e Duplication                         | 79         |

|       | 2.1.6         |      | UTL Basic Utilities                   | 80         |

| 2.2   |               |      | FTWARE                                | 83         |

|       | 2.2.1         |      | AL Assembler                          | 83         |

|       | 2.2.2         |      |                                       | 83         |

|       |               | -    | ration                                | 84         |

|       | 2.2.4         | Sou  | rce Program Format                    | 84         |

|       | 2.2.5         |      | abols                                 | 85         |

|       | 2.2.6         | Lite | erals                                 | 85         |

|       | 2.2.7         | *    | ressions                              | 86         |

|       | 2.2.8         | Ass  | embly Directives                      | 87         |

|       | 2.2.9         | Prog | gram Listing                          | <b>9</b> 0 |

|       | 2.2.10        | S16  | DGS Diagnostics                       | 91         |

|       | 2.2.11        | Usi  | ng S16AL                              | 92         |

| 2.3   | TEXT          | EDIT | DR                                    | 93         |

|       | 2.3.1         | Ope  | ration                                | 93         |

|       | 2.3.2         | Con  | nmands                                | 93         |

|       | 2.3.3         | Usi  | ng S16TXE                             | 96         |

| 2.4   | S16RLI        | LREI | OCATING LINKING LOADER                | 98         |

|       | 2.4.1         | Ope  | ration                                | 98         |

|       | 2.4.2         | Err  | or Messages                           | 99         |

| 2.5   | DIAGN         |      |                                       | 100        |

|       | 2.5.1         | CPU  | J-Memory Test                         | 100        |

|       | 2.5.2         |      | rrupt Test                            | 100        |

| APPEI | NDICES:       |      |                                       |            |

|       | A. S          | OFTV | VARE                                  | 101        |

|       | А             | 1    | Instruction Set                       | 101        |

|       | А             | 2    | Monitor Commands                      | 107        |

|       | A             | 3    | Sample Monitor Dialogue               | 108        |

|       | А             | 4    | Resident Utility Routines             | 113        |

|       | A             |      | Sample Assembly Listing               | 114        |

|       |               | 6    | Text Editor Commands                  | 117        |

|       |               | 7    | Sample Text Editor Dialogue           | 118        |

|       |               | 8    | Binary Tape Formats                   | 120        |

|       |               | 9    | S16RLL Sample Load Map                | 123        |

|       |               | . 10 | ASCII Character Codes                 | 124        |

|       |               | . 11 | Instruction Set Summary               | 125        |

#### TABLE OF CONTENTS

# APPENDICES GIC1600 MICROCOMPUTER SYSTEM (continued)

#### B. HARDWARE

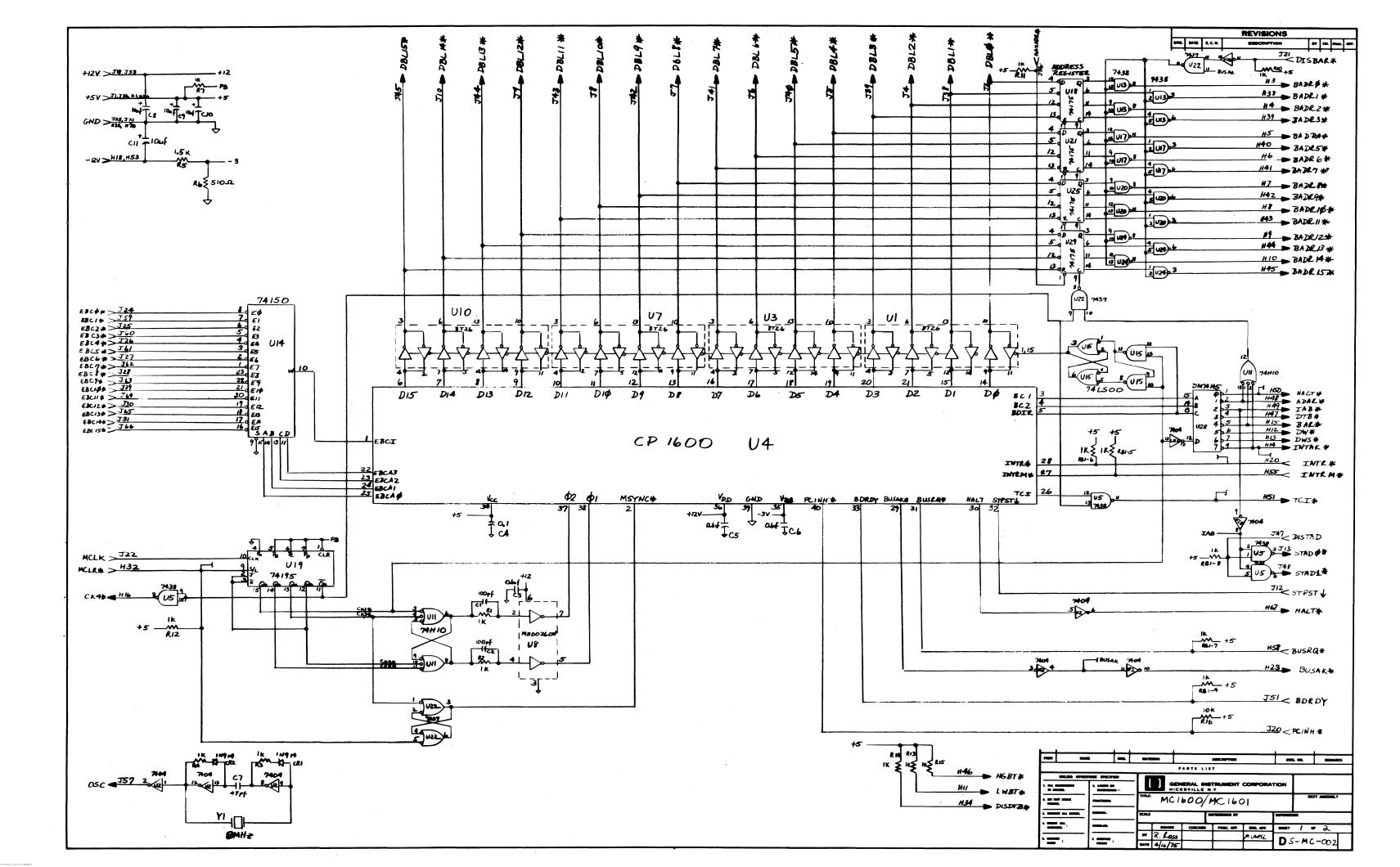

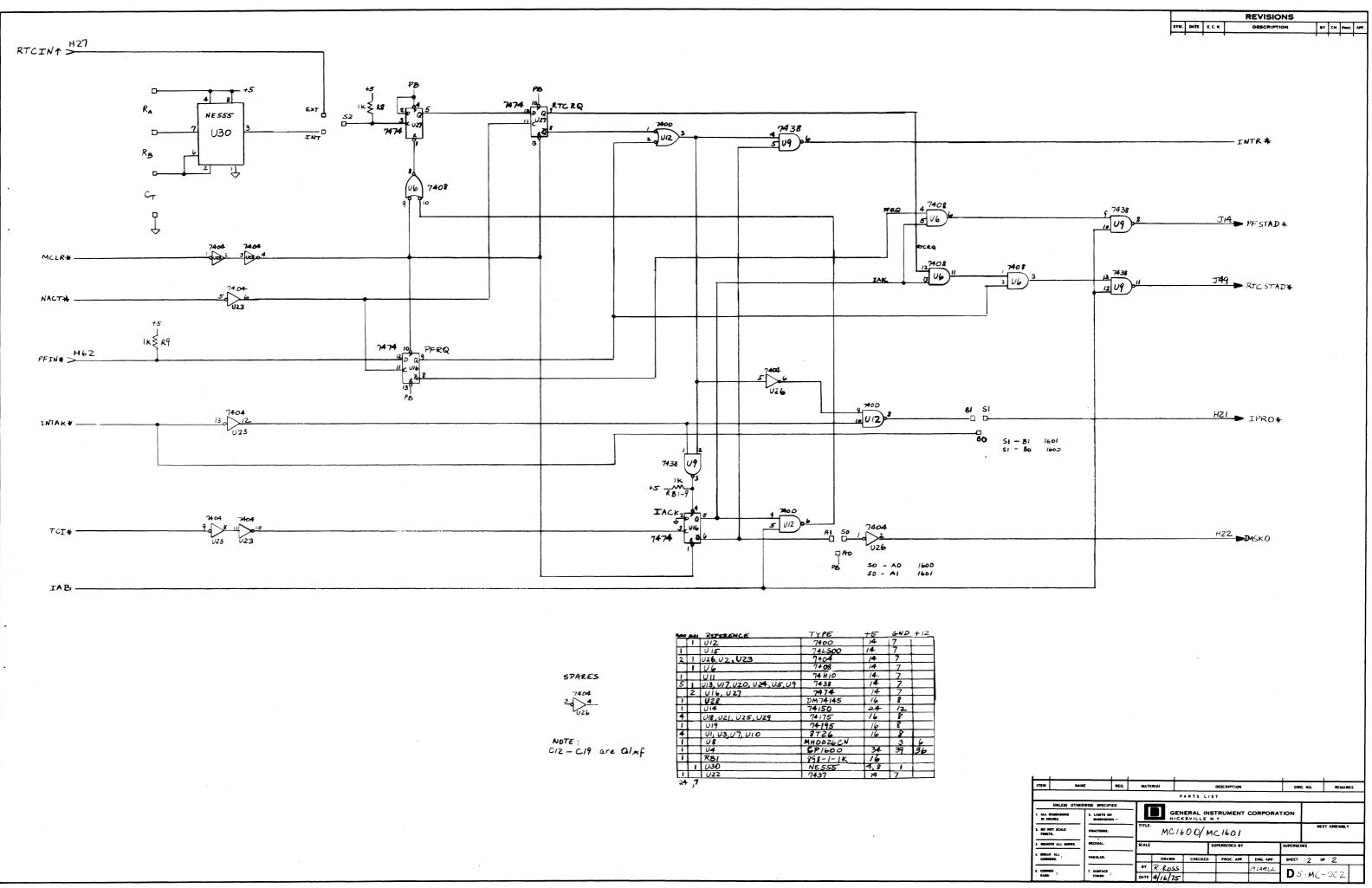

- B.1 MC1600/1601 Microcomputer Card Schematic DS-MC-002

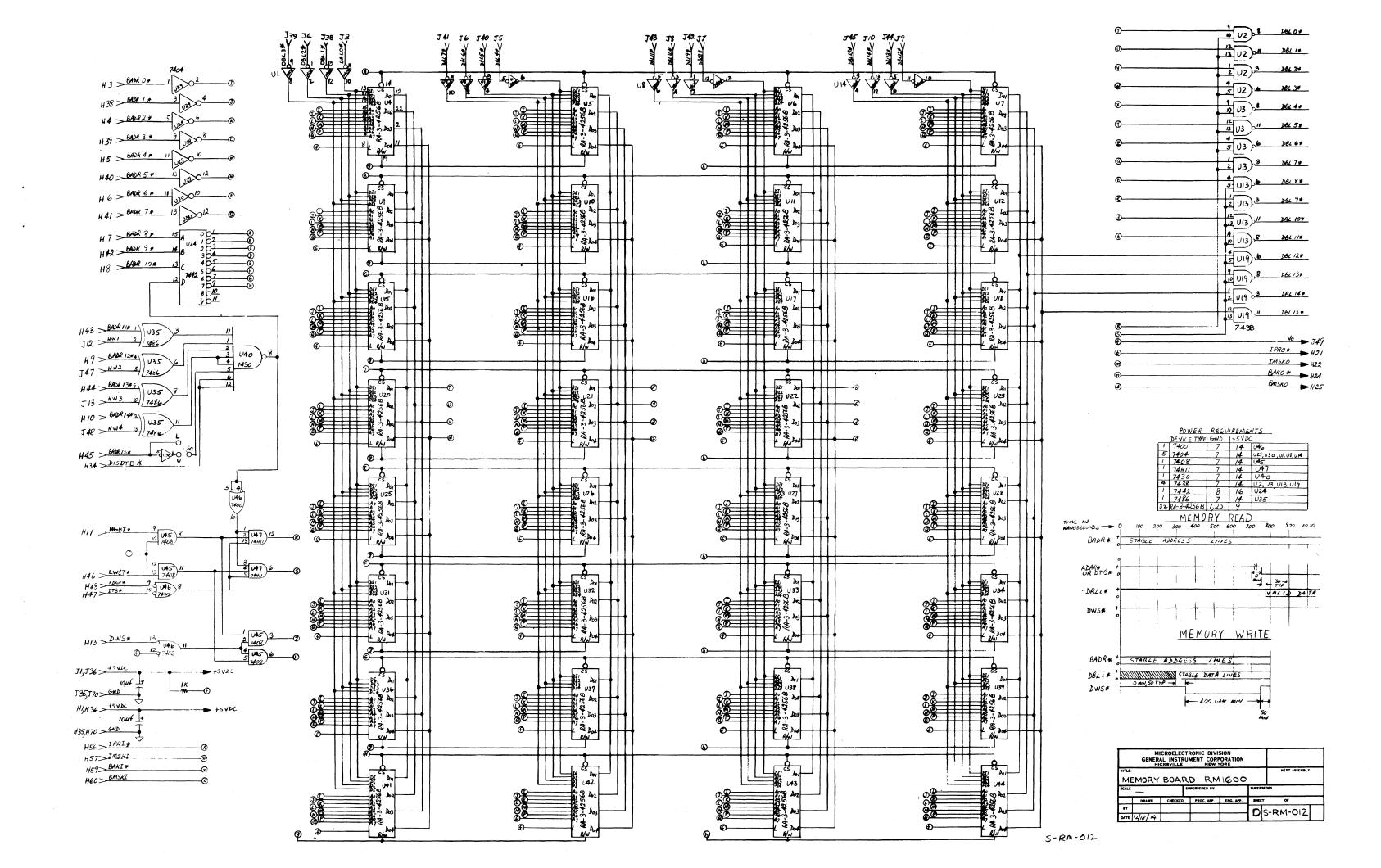

- B.2 RM1600 2K Memory Card Schematic S-RM-012

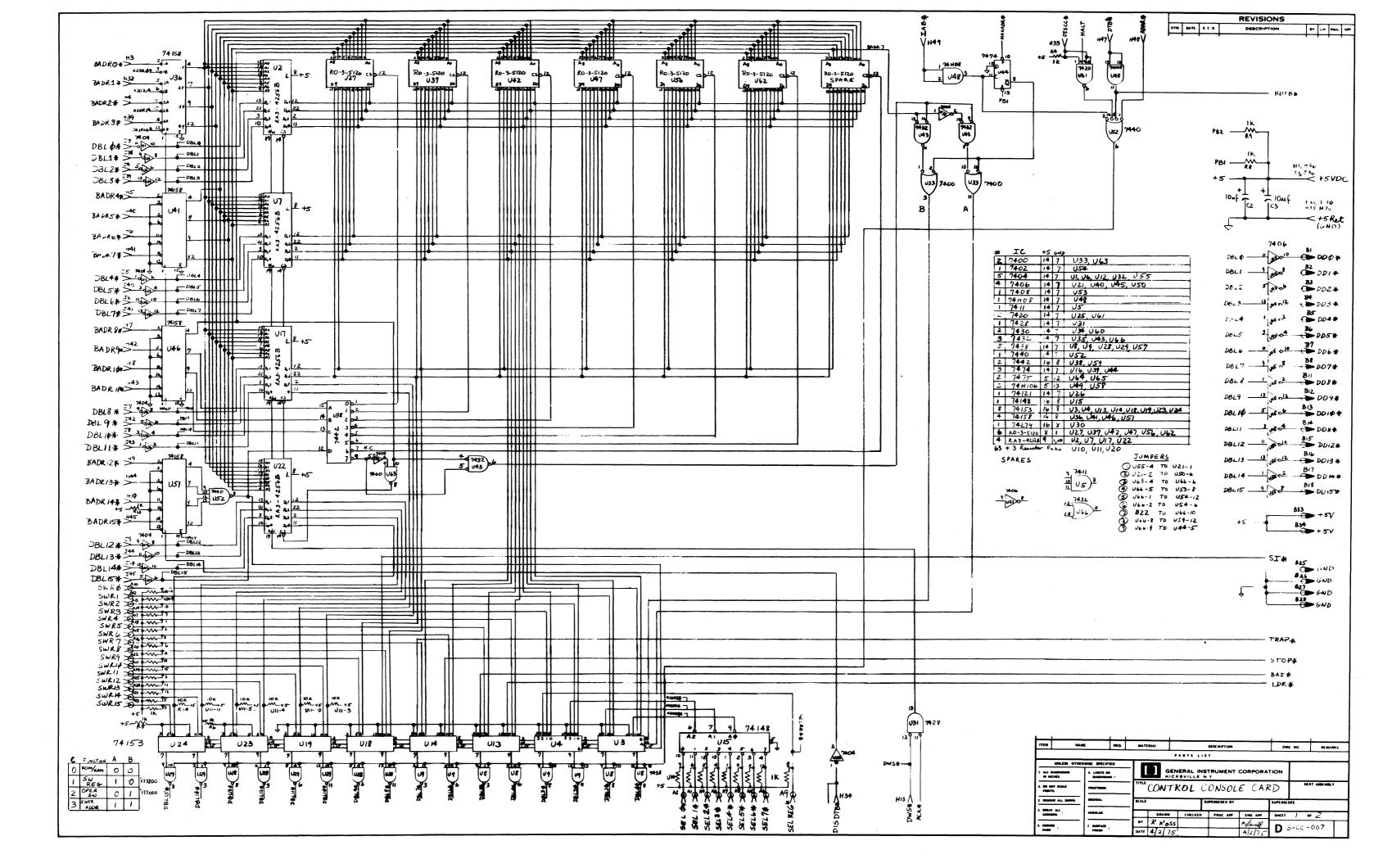

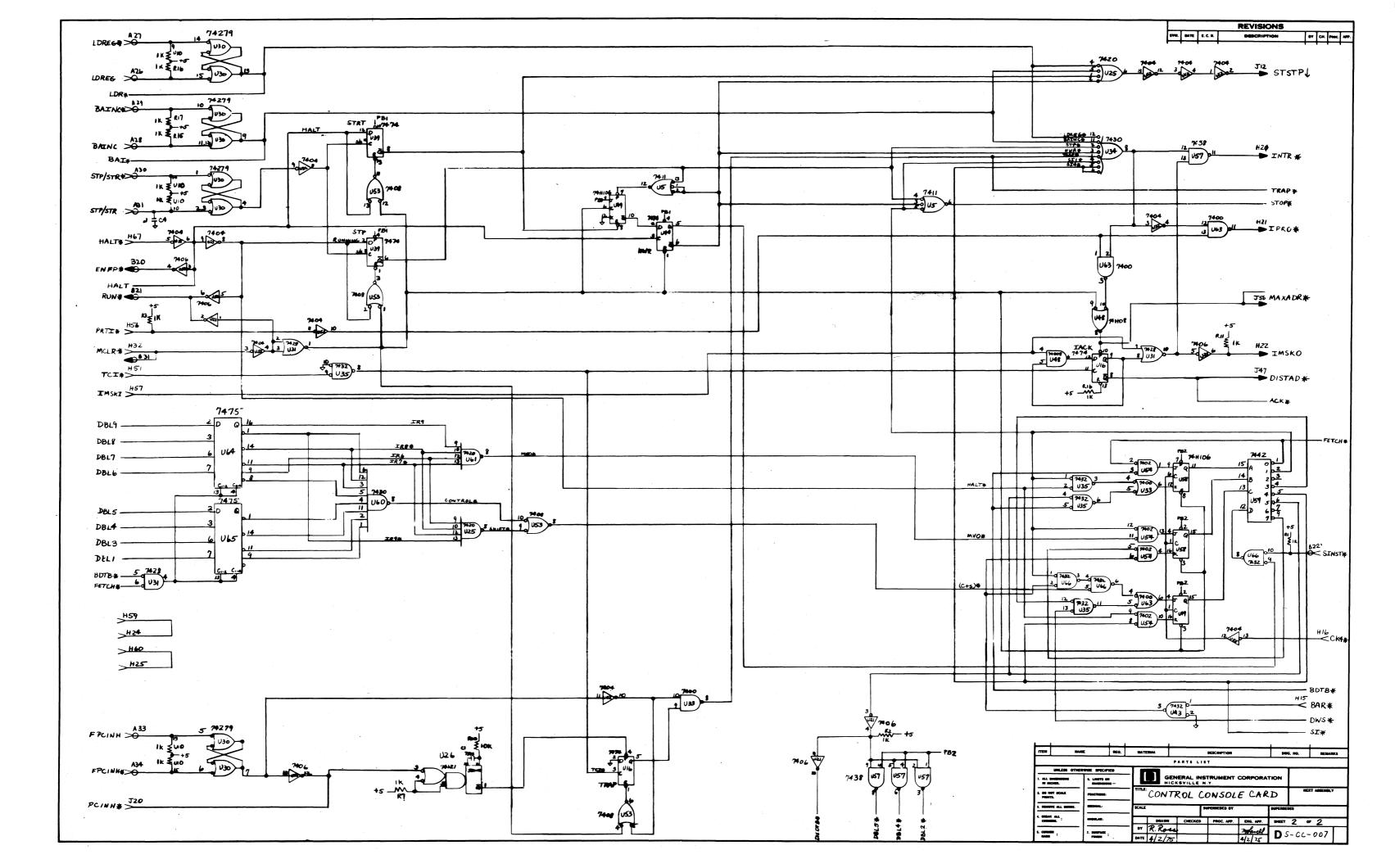

- B.3 CC1600 Control Console Card Schematic DS-CC-007

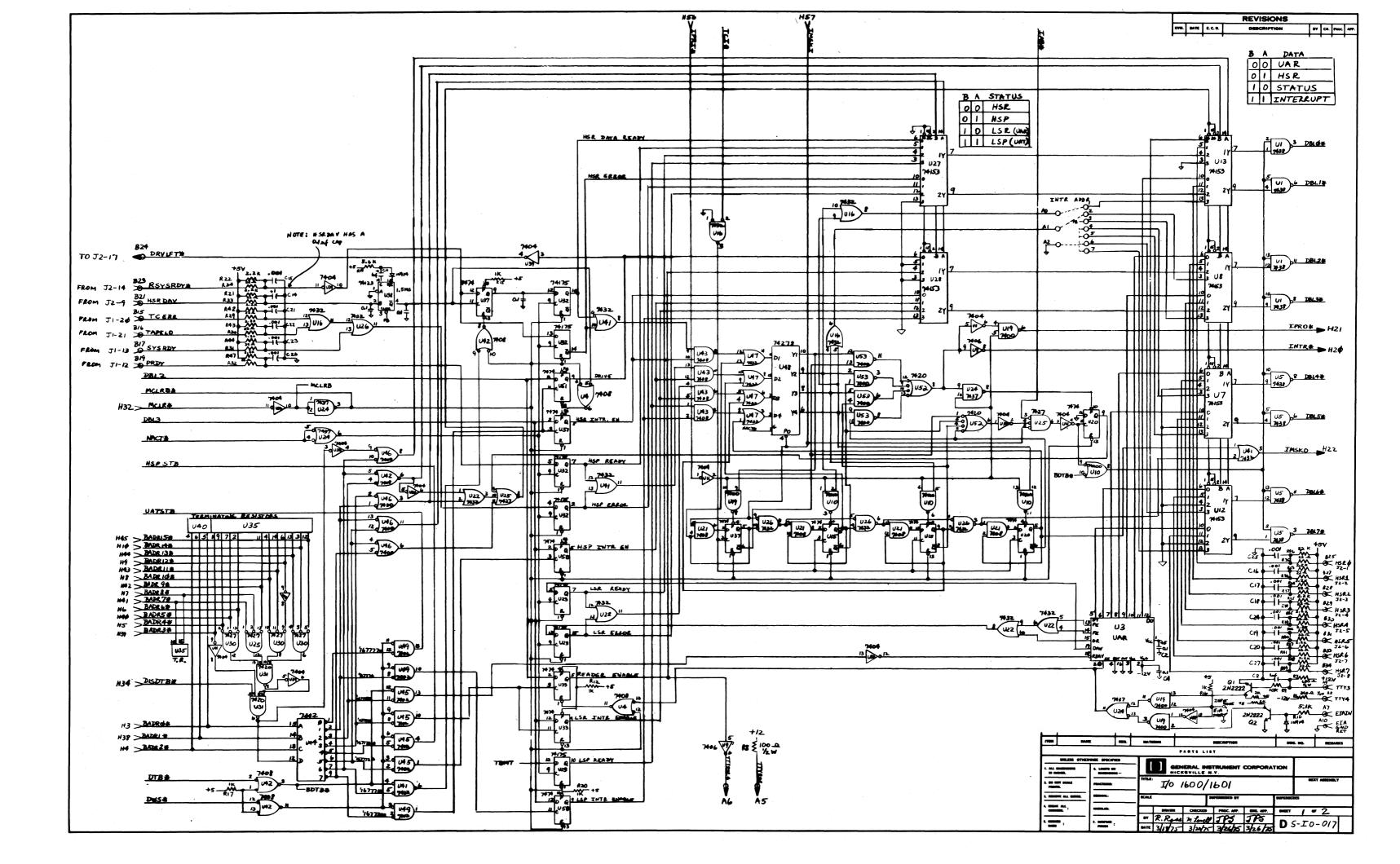

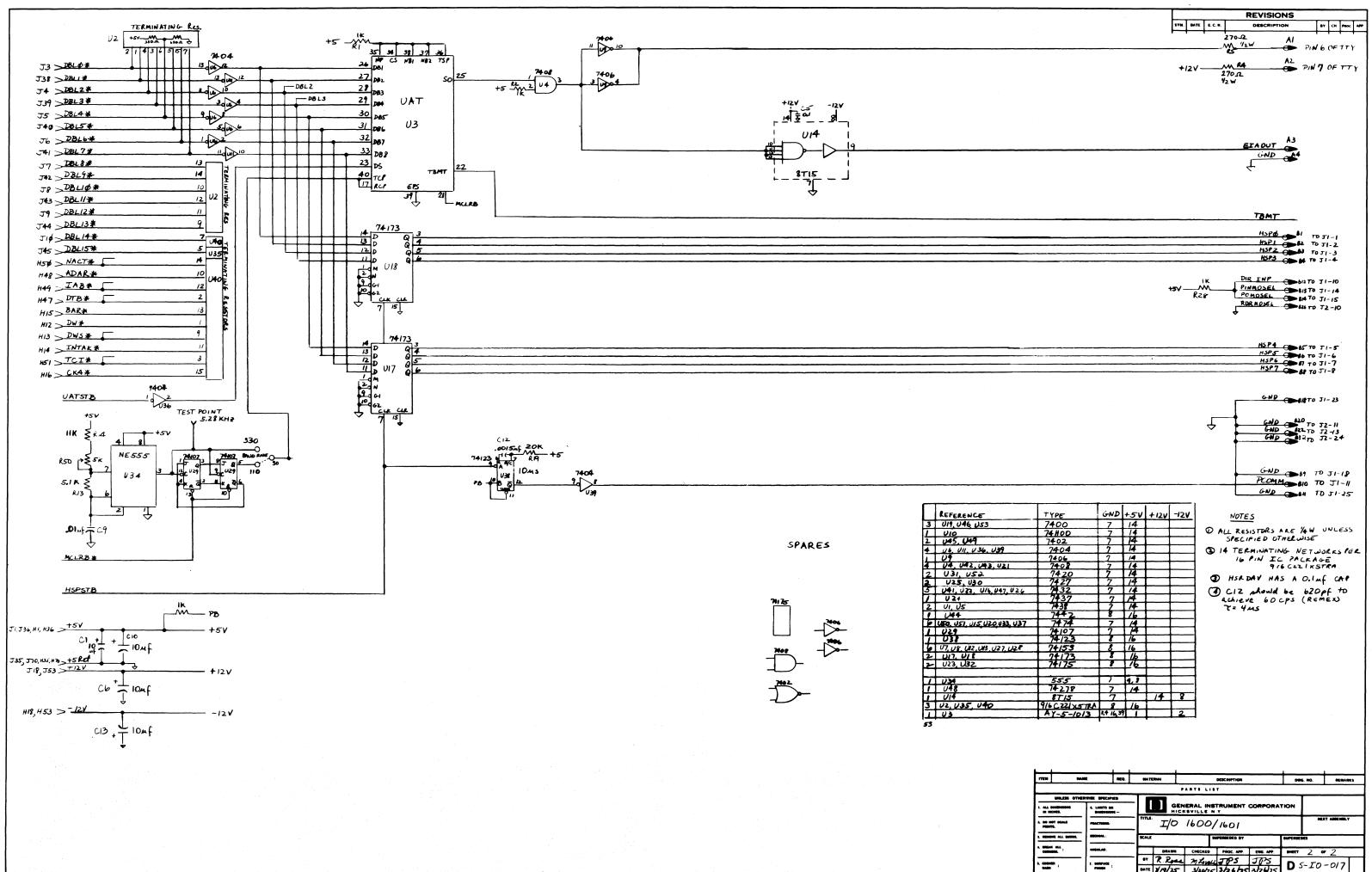

- B.4 I/O1600/1601 Input/Output Card Schematic DS-10-017

- B.5 GIC1600/1601 Interconnection Schematic S-BP-026

#### CHAPTER 1

#### GIC1600 SERIES MICROCOMPUTER USERS MANUAL

#### 1.0 INTRODUCTION

The GIC1600 Series Microcomputer Systems are general-purpose, stand-alone microcomputers built from the General Instrument family of OEM card level computer components. They are complete, self-contained development tools for both hardware and software prototyping and debugging. In addition, all the individual cards are fully-functional, stand-alone computer modules designed for easy integration into other systems.

The GIC1600 Series Microcomputer Systems are high performance 16-bit computers featuring direct addressing to 65K 16-bit words, a push down stack of unlimited depth, direct memory access (DMA), and a versatile nested interrupt system with priority resolution and self-identifying vectors. All control signals, data, and address buses are fully buffered and available on the backplane so the user can expand memory, add I/O capability, or develop and debug custom interfaces as required.

The GIC1600 Series Microcomputer Systems consist of a Central Processor Card, one or more RAM Memory Cards, an Input/Output Card, a Control Panel Card and Operators Console, and a Rack-Mountable Chassis. Additional cards may be added as required to expand the system capabilities and memory capacity.

In its standard configuration, each system can support a Teletype, a high speed paper tape reader/punch, and any RS232C compatible device, such as a Silent 700 Data Terminal. Additional interfaces and drive software as well as general purpose support cards are continually being added to the family. At present, a 4K PROM Card, additional 2K and 8K RAM Cards, and a General Purpose I/O Card are available as optional accessories.

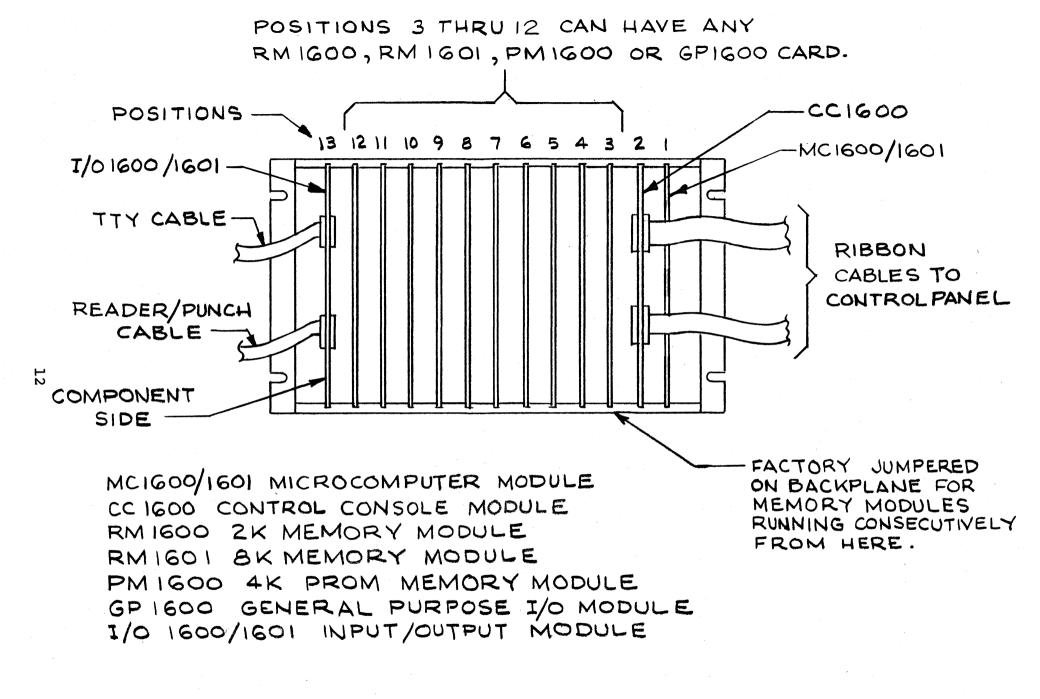

The Rack-Mountable Chassis and Printed Circuit Backplane has 13 positions for Wire-Wrap or Printed Circuit Cards, of which nine are available to the user for expansion of memory or special Input/Output interface. A general purpose Wire-Wrap Card is available so the user can easily design and construct his own custom interfaces and plug directly into any of the nine available positions in the chassis. Extender cards are also available to provide live access to the circuitry.

The GIC1600 Series Microcomputer System hardware and software provide the user with a versatile microcomputer system that is simple to configure to his individual application.

#### 1.1 SYSTEM DESCRIPTION

The GIC1600 Series Microcomputer Systems are supplied in three standard configurations. The GIC1600 includes a basic Microcomputer Module (MC1600), an 8K x 16 RAM Module (RM1601), a Control Panel Module and Operators Console (CC1600), an Input/Output Module (I/O1600), and a Chassis and Backplane Unit (CF1600). The GIC1601 is similar but includes a Microcomputer Module (MC1601) with Real Time Clock (RTC) and Power Fail Interrupt (PFI), and an Input/Output Module with RS232C capability (I/O1601).

#### 1.1.1 System Block Diagram

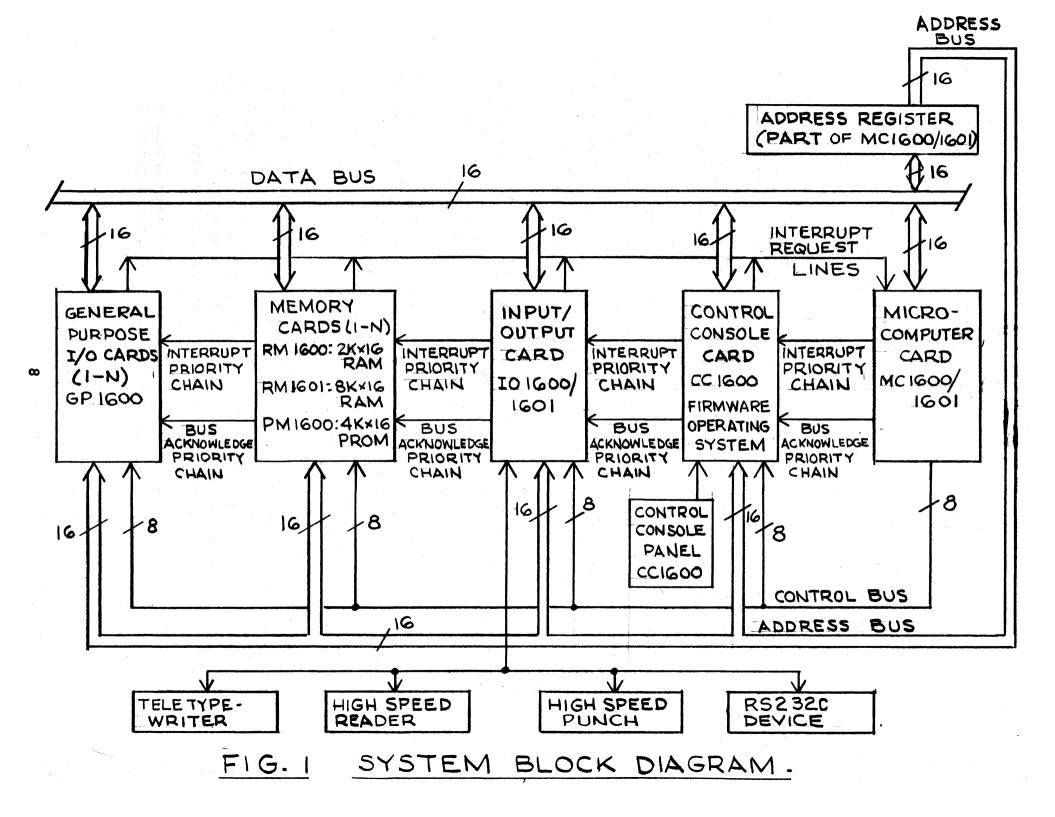

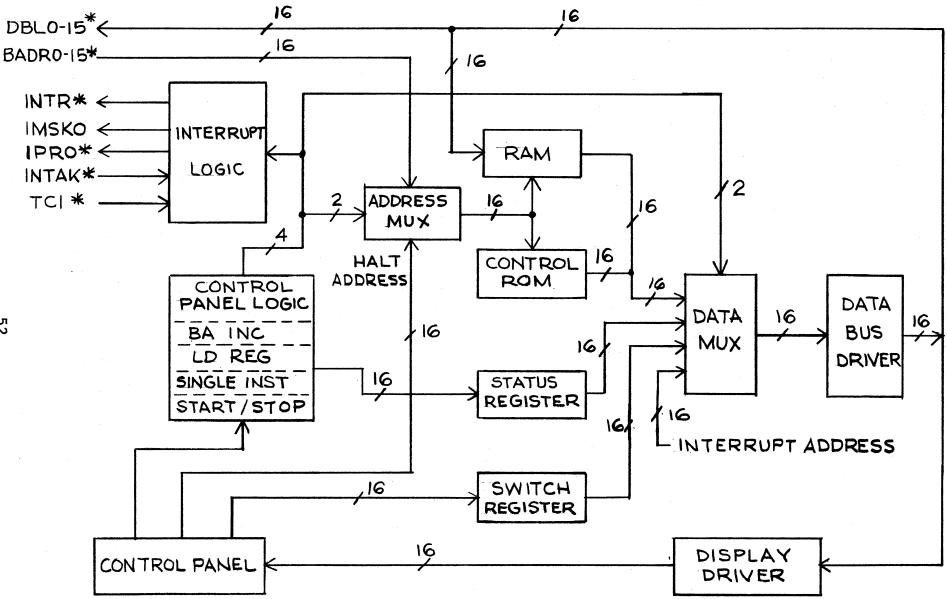

The basic system block diagram is shown in Figure 1. All microcomputer system components and peripherals connect to and communicate with each other on a common Data Bus. This bidirectional bus allows any device to send data to, receive data from, and exchange data with the central processor or any other device.

The Address Bus Register (part of the Microcomputer Module) captures and latches the address information from the Data Bus under the direction of the Microprocessor. The Address Bus lines are presented staticly to every module in the system for address decoding. The Microprocessor controls the time allocation of both the Data Bus and Address Bus via the Control Bus. The Control Bus contains eight control signals that direct all bus operations.

Any card in the system can issue an interrupt request to get Microcomputer service or a DMA request to gain access to the bus structure. The Microcomputer card acknowledges the request by issuing priority signals that are serially daisy-chained down the cards, establishing a priority assignment based on "electrical closeness" to the Microcomputer Module. The Microprocessor automatically resolves any simultaneity of requests by acknowledging DMA requests before interrupt requests.

#### 1.1.2 Basic System Modules

The MC1600 Microprocessor Module contains the CP1600 Microprocessor integrated circuit, the clock generator and crystal controlled oscillator, the Address Bus Register and buffers, the Data Bus transceivers, and the Control Bus Decoder/Driver. The MC1601 Microprocessor Module includes these items plus the Real Time Clock and Power Fail Interrupt options.

The CC1600 Control Console Module and Operators Panel monitors and directs all operations of the GIC1600 systems. A ROM resident program located on this card and occupying the top 4K of the 64K address space allows the user to perform an extensive set of front panel operations

FIG. 2. GIC 1600 SYSTEM MEMORY MAP.

such as read and punch tapes, display and modify memory and CPU registers, and execute programs, etc. In addition, the continuous or single instruct mode can be selected on the Operators Panel along with a unique "repeat instruction" function. Additional controls facilitating program debugging and hardware checkout are also provided on the Control Panel Console. In addition to all these manually controlled Operators Panel functions, the ROM Resident Operating System and Monitor Program provide total interactive control of the system via the Teletype. Beside the normal display and modifying of memory and CPU registers, the user can control the peripherals, load, copy, and punch tape, and set up to eight breakpoints in the active program.

The I/O1600 Input/Output Module provides full-duplex communication between the CPU and a Teletype and/or a High Speed Reader/Punch combination. The I/O1601 Input/Output Module provides the same capabilities plus the interface to any RS232C device such as a Silent 700 Data Terminal. The Silent 700 Terminal provides magnetic tape cassette offline storage and keyboard/printer capability which is a great convenience in program loading. Both I/O Modules contain fully character buffered controllers with all device timing and interrupt logic included.

The RM1600 RAM Memory Module contains 2048 words of 16-bit fully buffered RAM memory. The RM1601 Memory Module contains 8196 words of 16-bit RAM memory. Both include user-programmable Module Address Identification Logic so that several cards can be used together to build the memory to any desired capacity up to 65K words total.

The PM1600 PROM Memory Module and the GP1600 General Purpose Input/Output Module are available as additional options to the basic systems and are discussed in subsequent sections of this manual.

#### 1.1.3 System Memory Map

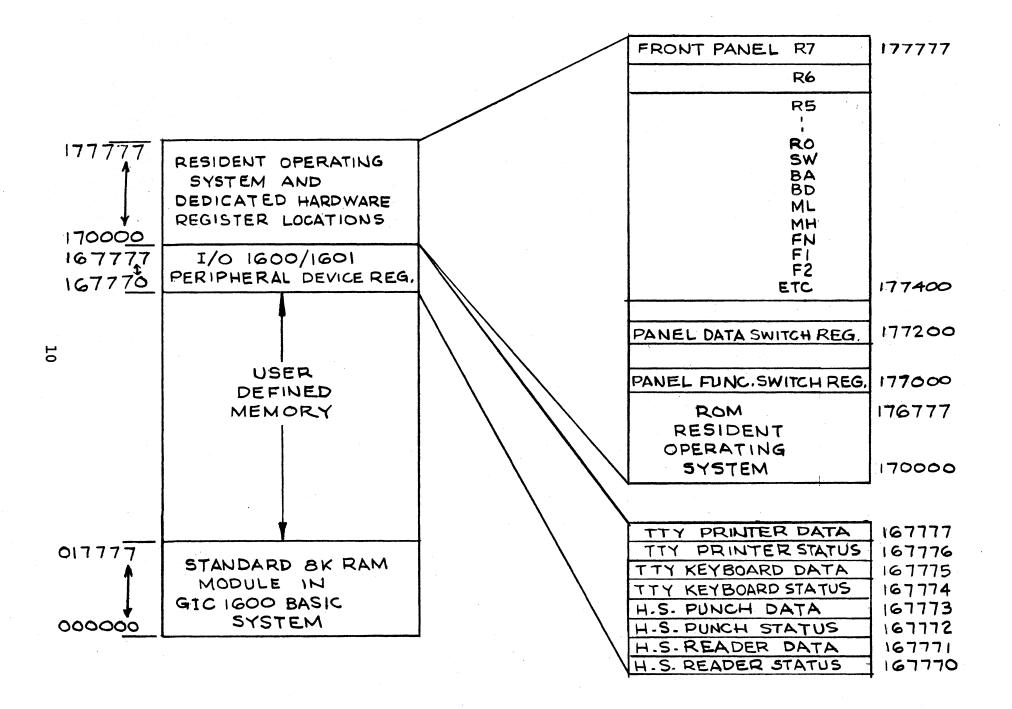

The memory map shown in Fig. 2 defines the allocation of the 65K memory space for the GIC1600 Series Microcomputer Systems. All but the upper 4K is user-defined.

The upper 4K of memory is reserved for the Resident Firmware Operating System, which is stored in ROM's on the Control Console Card. This set of programs start at address 170000 and are approximately 3K words long. Address location 177000 is used to access the Control Console Function Switches; address location 177200 is used to access the Control Console Data Switches. Memory locations 177400 to 177777 are RAM locations used for dynamic storage by the Resident Firmware Operating System.

FIG. 3. GIC 1600 MICROCOMPUTER CARD ASSIGNMENTS.

#### 1.2 SYSTEM SET-UP PROCEDURE

- a) Unpack system components and install Modules in the appropriate slots with the component side to the left as shown in Fig. 3. The system is factory wired via backplane jumpers for memory modules (RM1600 or RM1601) to occupy consecutive card positions starting from position 3 which always contains memory location zero.

- b) Connect power supply voltage and sense leads to the appropriately labeled terminals on the backplane of the microcomputer. The supplies should have the following current ratings:

+5V at 12A,  $\pm 5\%$ ; +12V at 1.5A, +5%; -12V at 0.5A, +5%

The supplies should have 0.1% load and line regulation and external sense capability. Use 16 AWG size wire for the +5V and +5V return leads.

- c) Establish the starting address of the Interrupt Branch Table by connecting J13 (STADØ\*) and J48 (STAD1\*) of the MC1600/1601 card position to the desired Data Bus lines; i.e., to establish 3000 as the start of the interrupt table connect J13 to DBL9\* and J48 to DBL10\* respectively. See Section 1.4.3 for further details.

- d) Connect the Teletype cable and the Reader/Punch cable to the I/O1600/1601 Input/Output Module in card position 13 as described in Section 1.5.1 and 1.5.2. The baud rate strap on the I/O1600/1601 card is factory wired for 110 baud. Modify the Teletype as explained in Section 1.5.1.

- e) Connect the Control Console Module cables to the Control Panel (the top connector on the card should be cabled to the right connector when facing the rear of the Control Panel).

- f) Turn on the power supplies. Push the MCLR switch and then the START/STOP switch. The Teletype will respond by typing: S16ODM V01B. The microcomputer system is now running and the Resident Operating System is awaiting a user command. (See Section 2.1.1).

#### 1.3 CONTROL CONSOLE

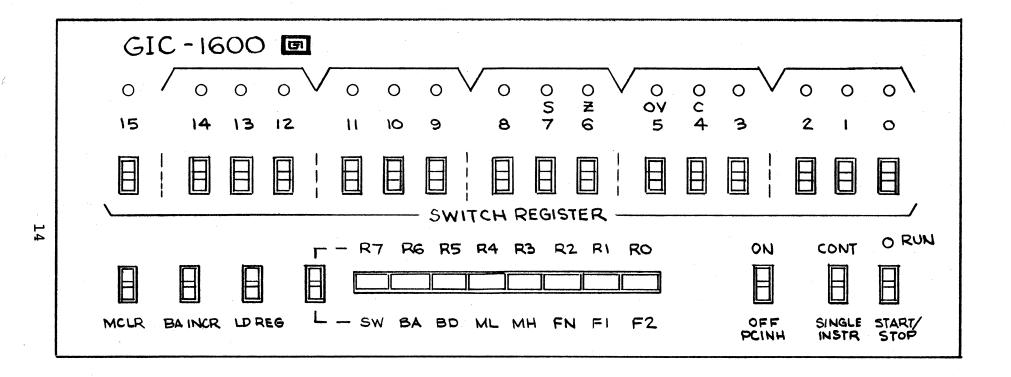

The GIC1600 Control Console is designed to provide a convenient method of controlling and monitoring the system. It is connected to the system via two cables that plug into the Control Console Interface Card (CC1600). Indicator lamps display the bus operation during the continuous run mode and display the contents of the registers while the CPU is halted. Various function and selection switches are also provided to allow complete control of the prototype system from the Operators Console. The GIC1600 Control Console is shown in Fig. 4.

## FIG. 4. CONTROL PANEL

#### 1.3.1 Control Console Description

The console has the following indicators and switches:

- 1) A RUN indicator light

- 2) A 16-bit Data Register Display

- 3) A 16-bit Switch Register

- 4) A set of 8 interlocked Register Select Switches to indicate one of 8 registers to be displayed.

- 5) A Register Bank Select Switch to indicate one of two banks of 8 registers each to be applied to the Register Select Switches.

- 6) Control Switches:

- a) LD REG: Load value set in Switch Register into selected register

- b) BA INC: Increment BA Register and update BD Register to reflect contents of new BA address

- c) MCLR: Master Clear

- d) PCINH: Inhibit incrementing of program counter during fetch phase to enable repetitive execution of a one word instruction

- e) CONT SINGLE INSTR: Mode of operation continuous or single instruction

- f) START/STOP: Toggle control for starting and stopping CPU

When the system is running a program, BAINC & LD REG are disabled to prevent any disruption of the operation. The PCINH switch should not be operated while the microcomputer is running.

#### 1.3.2 Control Console Functions

The console contains a 16-bit Switch Register that is capable of referencing a 16-bit address (i.e., 65K of memory space). A switch in the up position is considered to have a 1 value. A switch in the down position is considered to have a 0 value. The contents of the Switch Register can be loaded into any register by selecting that register on the Register Select and Bank Select Switches; it can be any one of the eight internal registers, R0 to R7, of the CPU or the SW, BA, BD, ML, MH, FN, F1 & F2 registers described below. After depressing LD REG, the contents of the selected register will be modified and the 16-bit Display Register will change to reflect the modification.

The lower bank of 8 front panel accessible registers contains a number of important and useful functions for the user. The Status Word (SW) of

the CPU contains four bits; they are located in bits 4 to 7 of a 16-bit word to correspond to their position in the CP1600 Microprocessor word. They are arranged as follows: Carry (C) in Bit 4, Overflow (OV) in Bit 5, Zero (Z) in Bit 6, Sign (S) in Bit 7. The remaining bits will always read 0 and are "don't care" when loading the SW from the front panel.

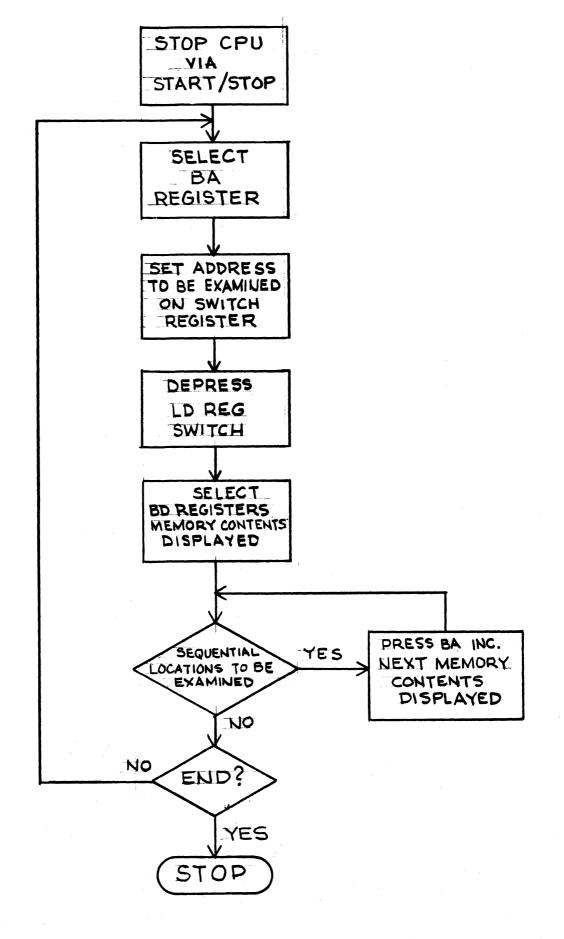

In order to provide the capability of accessing memory, two registers BA and BD have been assigned. Register BA contains a Bus Address and the contents of that bus location is displayed in the Bus Data Register BD. In order to examine a memory location, the address is first keyed into the Switch Register and BA is selected on the Register Select and Bank Select Switches. Pressing LD REG will then deposit the contents of the Switch Register into Register BA. The contents of the selected location (the address now held in BA) will automatically be loaded into Register BD. By selecting BD on the Register Select Switches, the contents of the memory address just loaded into BA will appear in the Display Register. Sequential memory locations can then be examined by depressing BAINC while BD is selected.

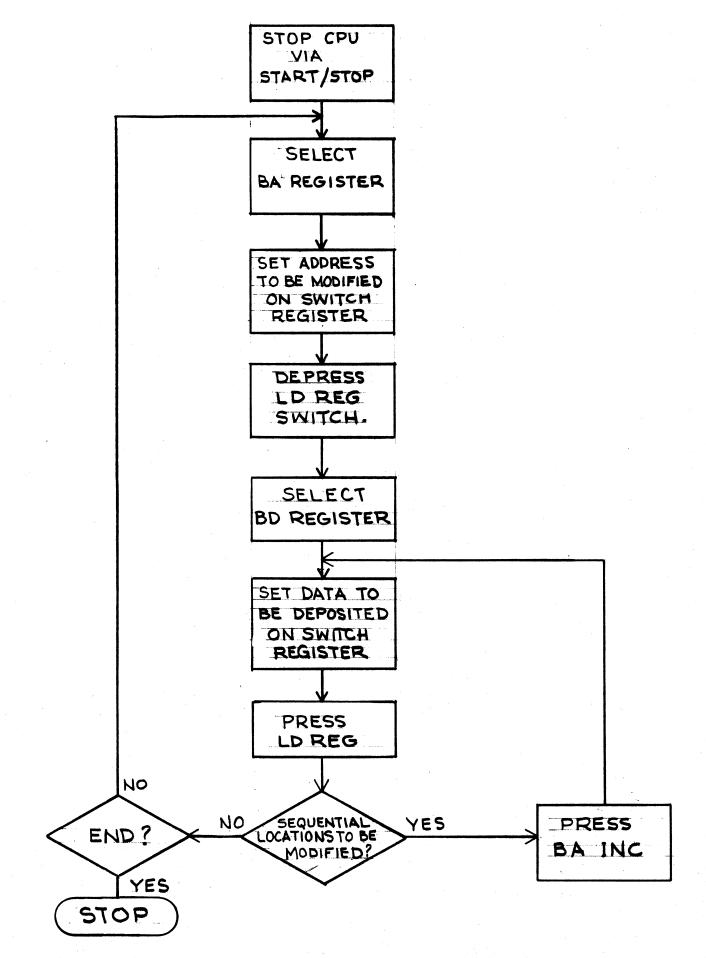

In order to modify any bus (memory) location the Bus Address must first be loaded into BA. Then BD is selected and the contents of that location will appear on the Data Display. The new data to be deposited is then keyed into the Switch Register. By depressing LD REG, the contents of the Switch Register will be deposited at the specified address held in BA and the Data Display will reflect the new data. Sequential memory locations can be written while BD is selected by depressing BAINC, updating the Switch Register to the new data, and then depressing LD REG.

The ML and MH registers are the Memory Low limit and the Memory High limit registers. The memory space between these two limits, which can be set by the user, is available for loading new programs. The memory space below the Memory Low limit and above the Memory High limit is protected from being overwritten during loading operations.

The FN (Function Number) register, the F1 register and F2 register can control the high speed reader/punch if a teletype is not available for communication with the Resident Firmware Operating System. After depressing MCLR, but before depressing START/STOP, select the desired operation by setting up these registers as follows:

- FN=1:Load program tapes via the high speed reader. If relocationis desired, set F1 to the relocation address. F2 is not usedin this mode.

- FN=2: Punch the contents of memory via the high speed punch. F1 is set to the low address; F2 is set to the high address.

- FN=3: Copy a tape via the high speed reader/punch. F1 and F2 are not used in this mode.

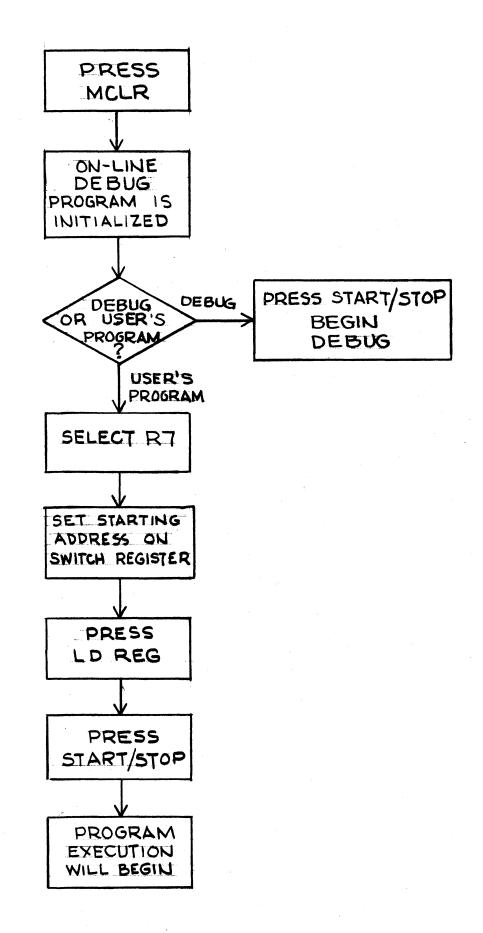

#### 1.3.3 GIC1600 Operation Via Control Console

Operation of the GIC1600 Series Microcomputer Systems must initially begin with the pressing of MCLR. This function initializes all internal hardware, supplies the starting address of the Resident Operating System to the PC (R7) and halts. Execution of the Resident Operating System begins by pressing START/STOP. If the user does not wish to enter the Operating System, the PC must be modified before pressing START/STOP. A new starting address must be keyed into the Switch Register, R7 selected and LD REG pressed. When START/STOP is pressed, the CPU will begin executing instructions at the supplied address.

The system can either be in CONT (Continuous) mode or SINGLE INSTR mode. In CONT, the system will free run until either a HALT instruction is executed or START/STOP is pressed. In SINGLE INSTR mode, the CPU will normally execute one instruction before halting. Depressing START/STOP repeatedly will allow single stepping through the program. The only instructions that have been designed to be bypassed in SINGLE INSTR mode are TCI and HLT. For these instructions the CPU will stop after executing the next instruction. (If, however, the following instructions are MVO, shift or control instructions, the CPU will stop after executing the first instruction that is not a MVO, shift, control, TCI or HLT instruction.)

#### 1.3.4 Operational Flow Charts

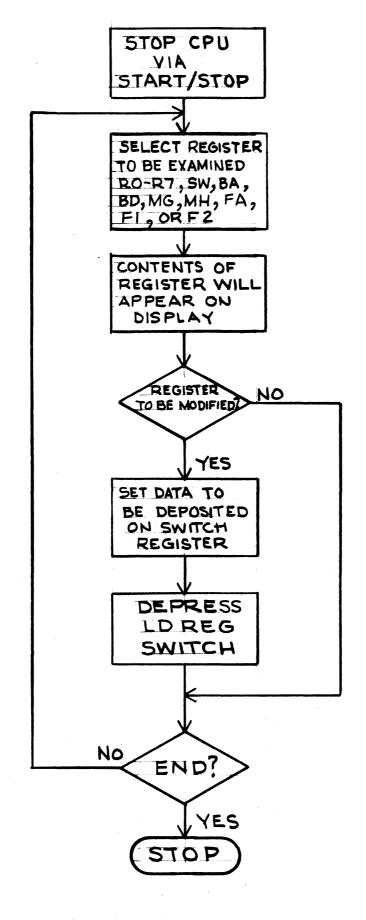

The diagrams shown in Figs. 5 to 8 depict step-by-step flow charts of the following procedures:

| Fig. | Procedure                                                     |

|------|---------------------------------------------------------------|

| 5    | GIC1600 Start Up Procedure                                    |

| 6    | Procedure to Examine Memory                                   |

| 7    | Procedure to Deposit New Data into Memory                     |

| 8    | Procedure to Examine and/or Modify the Internal CPU Registers |

#### 1.4 DATA, ADDRESS & CONTROL BUSES

The GIC1600 Series Microcomputer Systems have a Data Bus, an Address Bus, and a Control Bus which connect the microprocessor, the memory, and all the peripherals. The form of communication is the same for every device on the bus.

Since a single Address Space concept is utilized in the CP1600 microprocessor architecture, memory and peripheral devices reside within the same 65K Address Space. The system address allocation alone differentiates memory from I/O devices; there-

## FIG. 5 . GICIGOO START UP PROCEDURE.

## FIG. G. PROCEDURE TO EXAMINE MEMORY.

FIG. 7 . PROCEDURE TO DEPOSIT NEW DATA INTO MEMORY

## FIG. 8 . PROCEDURE TO EXAMINE AND/OR MODIFY THE INTERNAL CPU REGISTERS.

fore, no special I/O instructions are required and any External Reference instruction can access memory or peripheral devices. Peripheral devices in the system are addressed and operated upon by the software just as if they were memory locations. Since the GIC1600 Series Systems use a 16-bit address, the maximum Address Space is 65, 536 locations.

The Data Bus is bidirectional, i.e., the CPU can send data to, and receive data from, any peripheral device, such as a memory card, a Teletype, or a high speed reader/punch. The Address Bus is derived from latching the data on the Data Bus into the Address Register at the appropriate intervals of time, such as during the ADAR\*, BAR\*, and INTAK\* control pulse times.

The Control Bus provides eight buffered output control signals to define the function to be performed on the Data and Address Buses. These signals are used to control all communication between the microprocessor, memory, and all peripheral devices.

When a peripheral device requests bus control for Direct Memory Access (DMA), the Data, Address and Control Buses will enter a high output impedance state. This will enable a peripheral device to have complete control of the Data, Address and Control Buses for DMA operation or any other type of communication.

The Data, Address and Control Buses are buffered and available on the backplane of the chassis so the user can develop his own custom interface.

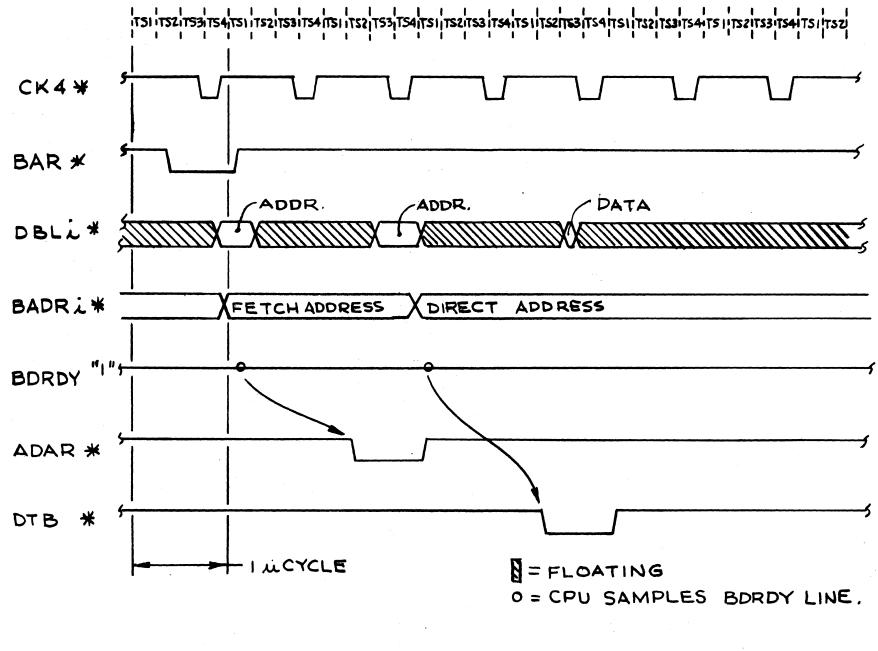

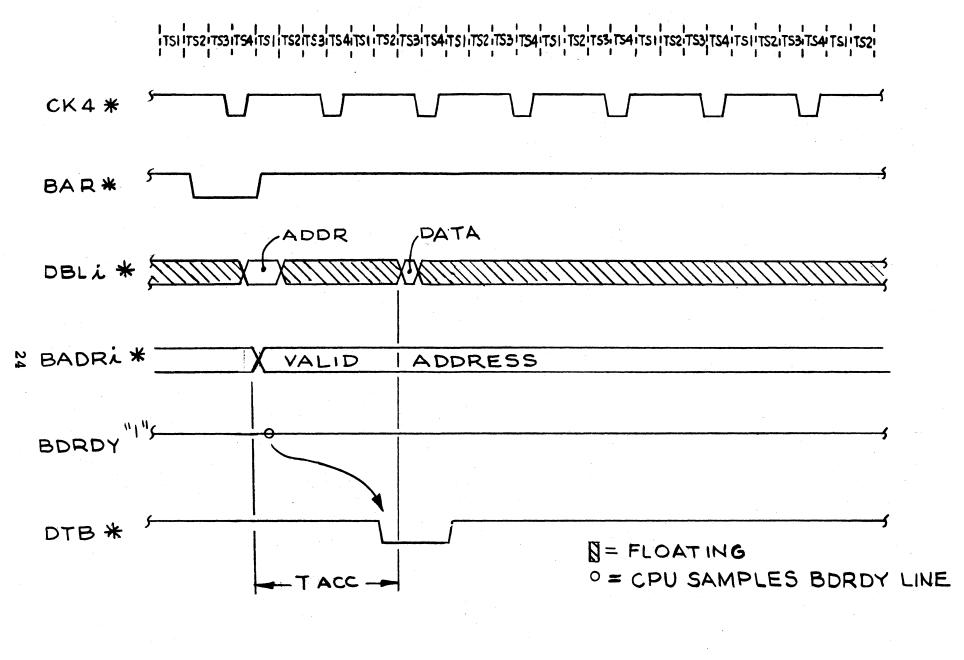

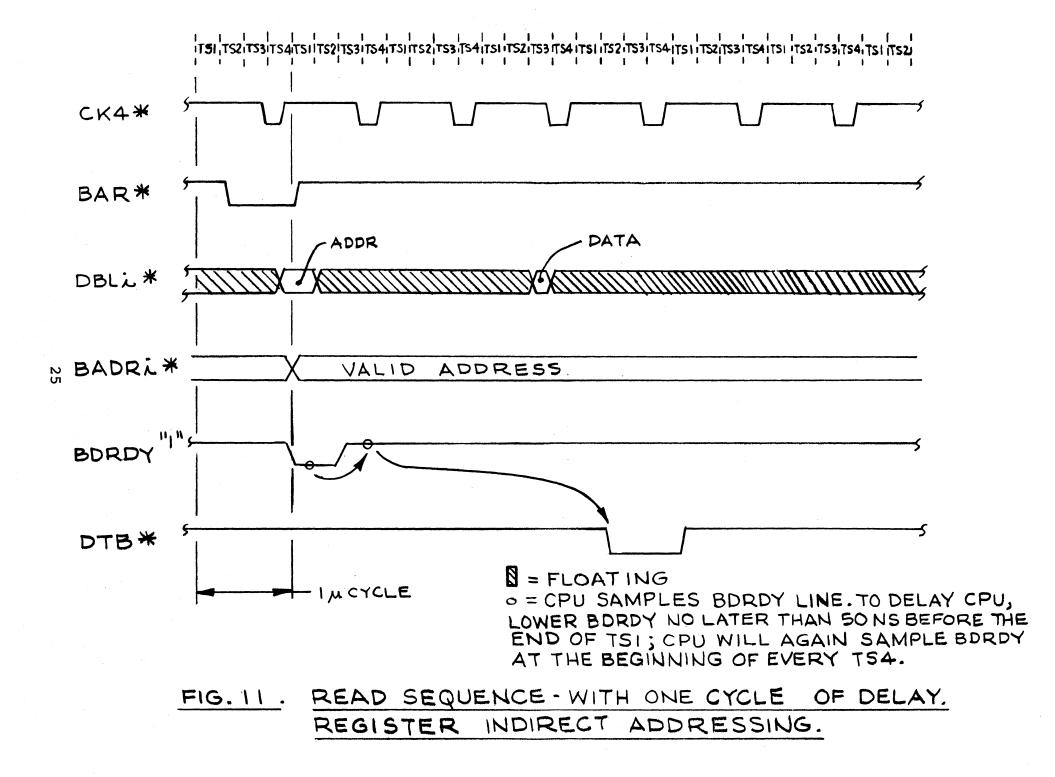

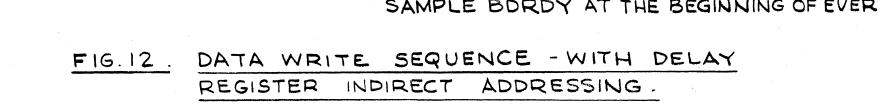

1.4.1 Backplane Signal Descriptions - Figs. 9-13 illustrate the use of these signals.

Data Bus

Data Bus Lines (DBL0-15\*)- Backplane Terminated

These 16 signals comprise the bidirectional bus that is used for all data communication. Since the CPU sends both data and address information to the external environment, the bus is also used to load the Address Register. The function to be performed on the data bus is determined under program control via the Bus Control signals. The Data Bus must be driven by open collector drivers capable of driving 30 TTL loads (7438 or equiv.).

Drive Capability: 18 TTL loads available to user.

#### Address Bus

Bus Address Register Lines (BADR0-15\*) - Backplane Terminated

These 16 output lines are used to select a peripheral device or an address location in memory. The address register is clocked in the middle of CK4\* during either ADAR\*, BAR\*, or INTAK\* and the address will

remain valid until the next clocking. The Address Bus is driven by open collector devices capable of driving 30 TTL loads. The lines are unidirectional and can also be driven under DMA operation with additional sets of open collector gates (7438 or equiv.) associated with the DMA device.

Drive Capability: 18 TTL loads available to user.

Control Bus

Bus to Address Register (BAR\*) - Backplane Terminated

This signal is used to load the Data Bus into the Address Register. It may be useful in informing peripherals that the Address Bus is valid by the trailing edge of BAR\*.

Drive Capability: 20 TTL loads available to user.

Data Write Strobe (DWS\*) - Backplane Terminated

This signal is used as a write enable for memory or any peripheral device. Data will be placed on the Data Bus 100ns prior to the leading edge of DWS\* and remain valid for at least 50ns after the trailing edge.

Drive Capability: 18 TTL loads available to user.

Data Write (DW\*) - Backplane Terminated

This signal is functionally identical to DWS\* except that it occurs one microcycle time prior to DWS\*. It may be used for extended writing operations.

Drive Capability: 21 TTL loads available to user.

Data to Bus (DTB\*) - Backplane Terminated

This signal is used to gate instructions, addresses, or data from memory or any peripheral device onto the Data Bus. If the data is to be input to the CPU, it must be stable at the microprocessor input pins within 80ns after the leading edge of DTB\* and remain valid for another 100ns.

Drive Capability: 20 TTL loads available to user

Interrupt Acknowledge (INTAK\*) - Backplane Terminated

This signal is generated by the CPU denoting its acceptance of an interrupt request and initiates the "daisy-chain" priority network to find and acknowledge the highest priority device presently requesting interrupt service.

Drive Capability: 19 TTL loads available to user.

Interrupt Address to Bus (IAB\*) - Backplane Terminated

This signal occurs during the Interrupt Sequence of the CPU. It occurs after the interrupt has been acknowledged and serves to gate the starting address of the service routine for the highest priority interrupting device onto the Data Bus. IAB\* also occurs after MCLR is depressed and during the power-up initialization sequence to input the starting address of the main program to the Program Counter. The address to be input to the CPU must be stable at the microprocessor input pins within 80ns after the leading edge of IAB\* and remain valid for another 100ns.

Drive Capability: 19 TTL loads available to user.

Addressed Data To Address Register (ADAR\*) - Backplane Terminated

This signal causes the addressed contents of memory to be gated onto the Data Bus and strobed into the Address Register. It is generated in response to all instructions which specify direct addressing.

Drive Capability: 19 TTL loads available to user.

No Action (NACT\*) - Backplane Terminated

This signal indicates that the CPU is not using the bus.

Drive Capability: 20 TTL loads available to user.

Other Backplane Signals

Terminate Current Interrupt (TCI\*) - Backplane Terminated

This signal, which is valid for one microcycle time, is generated by the execution of a Terminate Current Interrupt instruction in the program. It resets the highest priority interrupt presently being serviced and establishes priority at the next highest priority device which could be the main program if no other interrupts were in service or pending service.

Drive Capability: 19 TTL loads available to the user.

Clock Four (CK4\*) - Backplane Terminated

This signal is available to the user to synchronize external devices with Time Slot 4 of the CPU.

Drive Capability: 19 TTL loads available to the user.

External Branch Condition (EBC0 - 15\*) Microcomputer Input

The system provides input ports for 16 external conditions which can

be used as external branch conditions under program control.<sup>1</sup> The sense lines must be stable 100ns prior to examination by the CPU for proper branching. A "0" active input will result in branching.

Load: 1 TTL load

Bus Request (BUSRQ\*) - Microcomputer Terminated

The bus request line informs the processor that an external device requires the use of the Data Bus. The CPU grants the use of the bus after the completion of an interruptable instruction and responds with BUSAK\*. The microprocessor then becomes inactive with its Data Bus driver/receiver inactive and NACT\* active. The CPU will remain in this condition until the external device releases BUSRQ\*.

Load: 4 TTL loads

Bus Acknowledge (BUSAK\*) - Microcomputer Driven

BUSAK \* becomes active when BUSRQ\* is received by the CPU and the execution of the next interrutable instruction has been completed. This line will remain active as long as BUSRQ\* remains low. This signal serves to inform the requesting device that the processor has surrendered control of the Data Bus for DMA or non-processor controlled bus operations.

Drive Capability: 10 TTL loads available to user

Bus Data Ready (BDRDY) - Microcomputer Terminated

This signal permits resynchronization of the CPU for peripheral subsystems or memories that cannot respond to requests for reads and writes at full CPU speed. BDRDY must go low no later than 50nsec after the end of either BAR\* or ADAR\* for reading and DWS\* for writing in order to begin delay operation. The CPU then samples BDRDY at the leading edge of TS4 for additional delay. The duration of the wait period must be less than 40 microseconds to preserve the dynamic status of the CPU.

Load: 4 TTL loads

Interrupt Request (INTR\*) - Microcomputer Terminated

This line is the higher priority interrupt request line of the two interrupt request lines. It is not affected by the state of the interrupt mask F/F within the CPU. The CPU will honor the request only after the completion of the next interruptable instruction. The user should remove the INTR\* being generated by a device after the CPU acknowledges that device's request with INTAK\*.

Load: 4 TTL loads

Interrupt Request Maskable (INTRM\*) - Microcomputer Terminated

This line is the lower priority of the two interrupt request lines. It is effective in generating an interrupt only if the interrupt mask F/F within the CPU has been cleared. The interrupt mask F/F is accessable under program control via the Enable Interrupt System (EIS) and Disable Interrupt System (DIS) instructions.

Load: 4 TTL loads

Disable Bus Address Register (DISBAR\*) - Microcomputer Terminated

This signal is used for DMA operation. A logical "0" input applied to DISBAR\* will float the Address Bus whenever the CPU has acknowledged a BUSRQ\* signal with BUSAK\*.

Load: 4 TTL loads

Halt (HALT\*) - Microcomputer Driven

This signal indicates that the CPU is in the stopped mode. This mode can occur either by the toggle action from the START/STOP Switch on the front panel or by the execution of a HALT instruction.

Drive Capability: 9 TTL loads available to user

Stop/Start (STPST) - Microcomputer Input

This is a negative edge-triggered signal used to control the running condition of the CPU. If the CPU is presently running, the negative transition of STPST will cause the CPU to stop but only after the completion of an interruptable instruction. The CPU will generate a high active HALT signal indicating the stopped condition. The next negative transition of STPST will cause the CPU to return to the run mode. The HALT output will then return to a logic "0" (low) condition.

Note: The STPST signal is used for Control Console operation only.

<u>Master Clear</u> (MCLR\*) - Microcomputer Terminated

This signal is used to initialize all internal hardware and reset the internal timing of the processor to its starting condition. MCLR\* is hardwired to the front panel switch MCLR but may also be "wire-or" connected to any peripheral device's MCLR\* signal to initialize the device to a known state.

Load: 4 TTL loads

Disable Data to Bus (DISDTB\*) - Control Console Driven

This signal is generated by the control console card to disable all memory and peripheral devices from interfering with bus operations at certain critical times. For proper control console operation every I/O device must use this signal to disable its address decoder.

Drive Capability: 1 TTL load

High Byte (HGBT\*) - Microcomputer Terminated

This signal is used during the reading of RAM memory. A logic "0" applied to HGBT\* will mask out the lower byte (Bits 0-7) of an addressed memory location from outputting onto the Data Bus. The high byte (Bits 8-15) will not be effected. This signal is not used in the GIC1600 Systems and is permanently tied high (inactive) on the Microcomputer Module.

Low Byte (LWBT\*) - Microcomputer Terminated

This signal is used during the reading of RAM memory. A logic "0" applied to LWBT\* will mask out the higher byte (Bits 8-15) of an addressed memory location from outputting onto the Data Bus. The low byte (Bits 0-7) will not be effected. This signal is not used in the GIC1600 Systems and is permanently tied high (inactive) on the Microcomputer Module.

Interrupt Priority In (IPRI\*)

Daisy-Chained Card to Card

Interrupt Priority Out (IPRO\*)

These two signals are used to resolve interrupt device priority and to allow INTAK\* to acknowledge only the highest device.

Interrupt Mask In (IMSKI)

Interrupt Mask Out (IMSKO)

Daisy-Chained Card to Card

These two signals are used to mask out all lower priority devices from

requesting an interrupt while a higher device is being serviced.

Bus Acknowledge In (BAKI\*)

Daisy-Chained Card to Card

Bus Acknowledge Out (BAKO\*)

These two signals are used to resolve DMA priority and to allow BUSAK\*

to acknowledge only the highest peripheral request.

Bus Mask In (BMSKI)

Bus Mask Out (BMSKO)

Daisy-Chained Card to Card

These two signals are used to mask out all lower priority devices from requesting use of the bus while a higher device has bus control.

Program Counter Inhibit (PCIT\*) - Microcomputer driven and Terminated

This signal provides two functions:

- a) As an input, this signal is a low active signal that prevents the incrementing of the Program Counter (R7) during the fetch phase of all instructions.

- b) As an output, this signal will generate a low active pulse during the execution of the SIN (Software INterrupt) instruction. This signal is received by the Control Console Card which in turn generates an interrupt request on the INTR\* line. This interrupt request is acknow-ledged at the end of the SIN instruction resulting in a jump into the Resident Operating System (TRAP function). These functions are designed so that they will not interact with each other under normal operation of the system.

Note: The PCIT\*signal is used for Control Console operation only.

#### 1.4.2 Direct Memory Access Operation

The GIC1600 Series Microcomputer Systems have the capability to handle high speed data transfers via DMA operation. External devices requesting DMA service must activate BUSRQ\* and then take control of the Data Bus when the CPU transmits back the BUSAK \* signal. When the device receives BUSAK\*, the interface can perform high speed transfers at speeds limited only by the memory system cycle time. The interface has the option of doing address and data transfers sequentially over the Data Bus using the Bus Address Register on the Microcomputer Module as a temporary address buffer. It can also do address and data transfers in parallel driving both Data and Address Buses at the same time. In order to use the parallel mode, the device must activate DISBAR \* (Disable Bus Address Register) which disconnects the Bus Address Register from the Address Bus so that it can be driven externally. In either case, the external device must drive the Control Bus signals (except for NACT\* which is always driven by the CPU when it is not using the bus) to define the bus operation during DMA cycles. The external device thus becomes bus master and is responsible for complete timing and control of information transfers on the Data Bus.

All Data Bus, Address Bus and Control Bus signals from the GIC1600 Series Microcomputers are in a high-output impedance state during a DMA operation. The NACT\* signal provides a 375ns pulse every microcycle time which can be utilized by the external device for DMA control. In addition, the Microcomputer Module also provides a CK4\* pulse every microcycle for additional timing flexibility. If more than one external device requests DMA operation, priority associated with these devices is handled via BAKI\*/BAKO\* and BMSKI/BMSKO priority daisy-chain networks located on the device controllers.

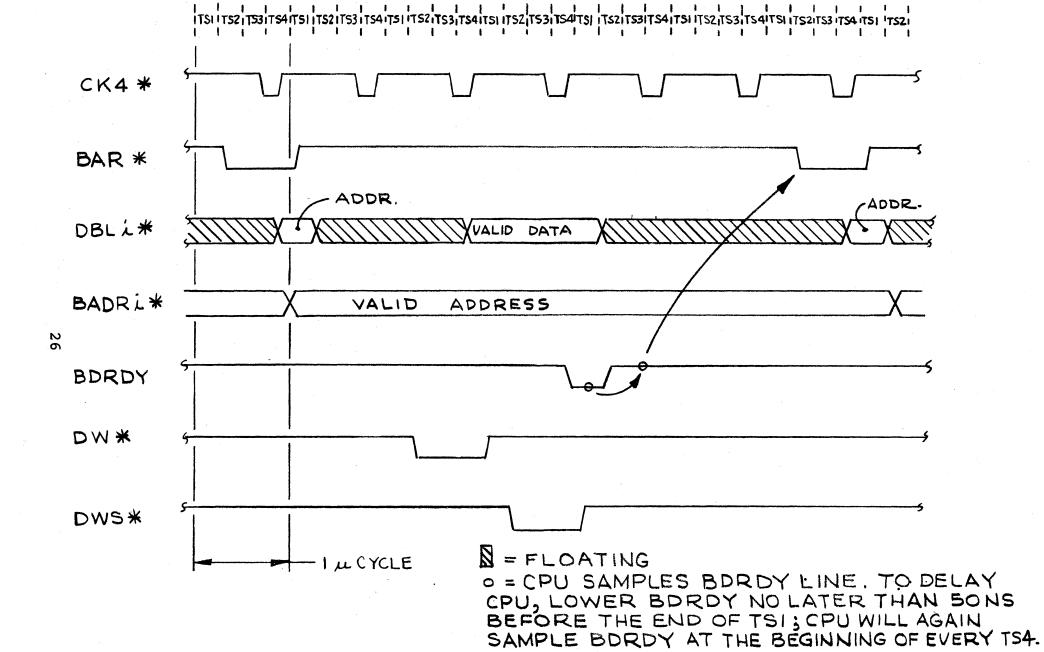

#### 1.4.3 Interrupt Operation

The GIC1600 Microcomputer System has two programmable interrupt lines, INTR\* and INTRM\*. These signals request the CPU to honor an interrupt at the completion of any interruptable instruction under the following conditions:

- a) INTR\* is always honored by the CPU and hence is the highest priority interrupt request line.

- b) INTRM\* is honored by the CPU only if the internal CPU interrupt flip-flop is enabled.

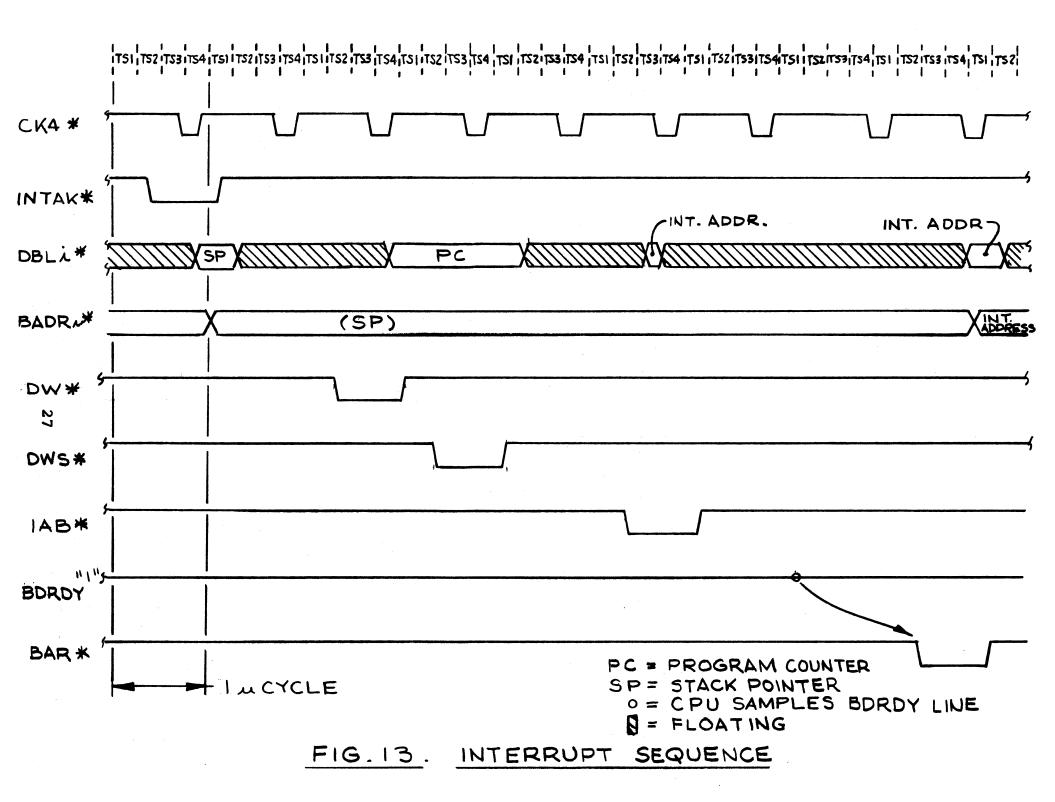

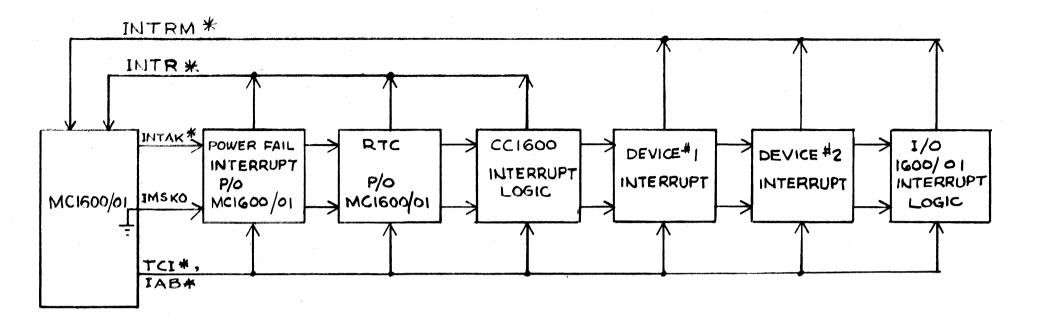

The GIC1600 Systems acknowledge either INTR\* or INTRM\* by giving an INTAK\* signal to the peripheral devices. This is followed by an IAB\* signal to bring the starting address of the interrupt service routine for the acknowledged interrupting device into the Program Counter of the CPU. All interrupt system servicing is handed via hardware/software combination. Refer to Device Interrupt Logic shown in Fig. 14.

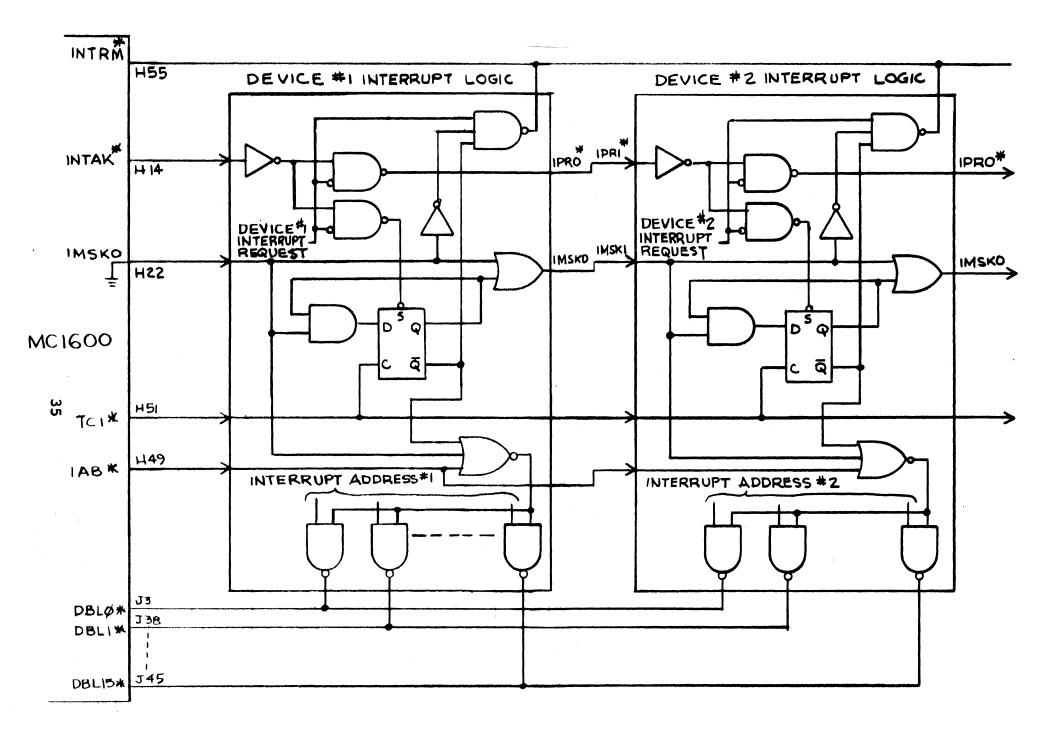

In order for peripheral devices to resolve priority, each device has a priority chain set-up as shown in Figure 15. Each device connects to the Interrupt Request line in order to request an interrupt operation. The CPU acknowledges the interrupt request by sending an interrupt acknowledge pulse, INTAK\*, to the first device in the interrupt priority daisy-chain network. The pulse proceeds down the chain from IPRI\* to IPRO\* of each device until it finds the device requesting an interrupt. This device then becomes acknowledged, blocks the priority pulse from further propagation, and sends out a mask signal IMSKO that propagates to all lower devices via the IMSKO to IMSKI chain. The mask chain insures that no lower priority devices can interrupt the service of the acknowledged device. The CPU then issues an IAB\* signal to all devices; however, only the highest priority device presently acknowledged uses this signal to present the starting address of its service routine to the Data Bus. This starting address is then strobed into the Program of the CPU.

# FIG. 14 DEVICE INTERRUPT LOGIC .

The basic GIC1600 Series Microcomputer Systems are factory wired such that the Power Fail Interrupt & Real Time Clock (on MC1601) are connected to INTR\* followed by the Control Console Interface Interrupt. All additional peripherals are wired into the priority chain as the user desires. The interrupt logic on I/O1600/1601 is wired to have the lowest order priority.

Once a device is connected to INTRM\* rather than INTR\*, all lower order priority devices must be connected to INTRM\* also.

# FIG. 15. INTERRUPT SYSTEM CONNECTION.

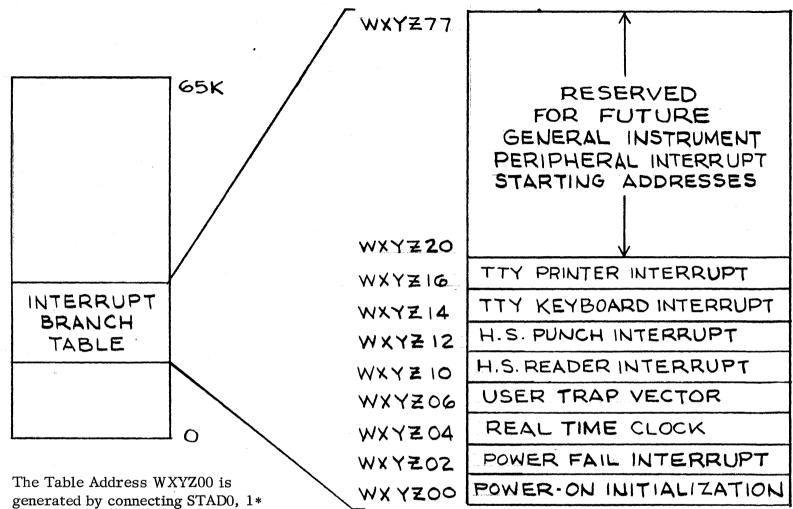

to any two DATA BUS LINES (DBL) between DBL6 and DBL15. The device identification code is contained in the lower six bit positions. W, X, Y, Z are octal numbers representing where STAD0, 1\* are connected; e.g. 014000 would indicate that STAD0, 1\* are connected to DBL11 & DBL12.

Each Interrupt Vector is 2 words normally containing a BRANCH or JUMP instruction to the start of the service routine.

FIG.16, INTERRUPT BRANCH TABLE

The interrupt addresses supplied by the peripherals in the GIC1600 Systems are arranged to be consecutive entries into an Interrupt Branch Table. Each entry in this table consists of two words which normally contain a BRANCH instruction to direct the CPU to the appropriate service routine. The Interrupt Branch Table can be located anywhere in memory and is defined by the connection of J13 (STADO\*) and J48 (STAD1\*) to the appropriate Data Bus lines (DBL0-15\*). The interrupting device generates a unique code defining the low order part of its interrupt address and the IAB\* signal automatically gates STADO\* and STAD1\* defining the upper part of all interrupt addresses. The result is an Interrupt Branch Table as shown in Fig.16.

At the completion of the interrupt service routine, the CPU generates a Terminate Current Interrupt signal, TCI, to reset the current interrupt (highest priority interrupt presently being serviced) and re-establish priority at the next lowest device needing service.

## 1.5 PERIPHERAL OPERATION

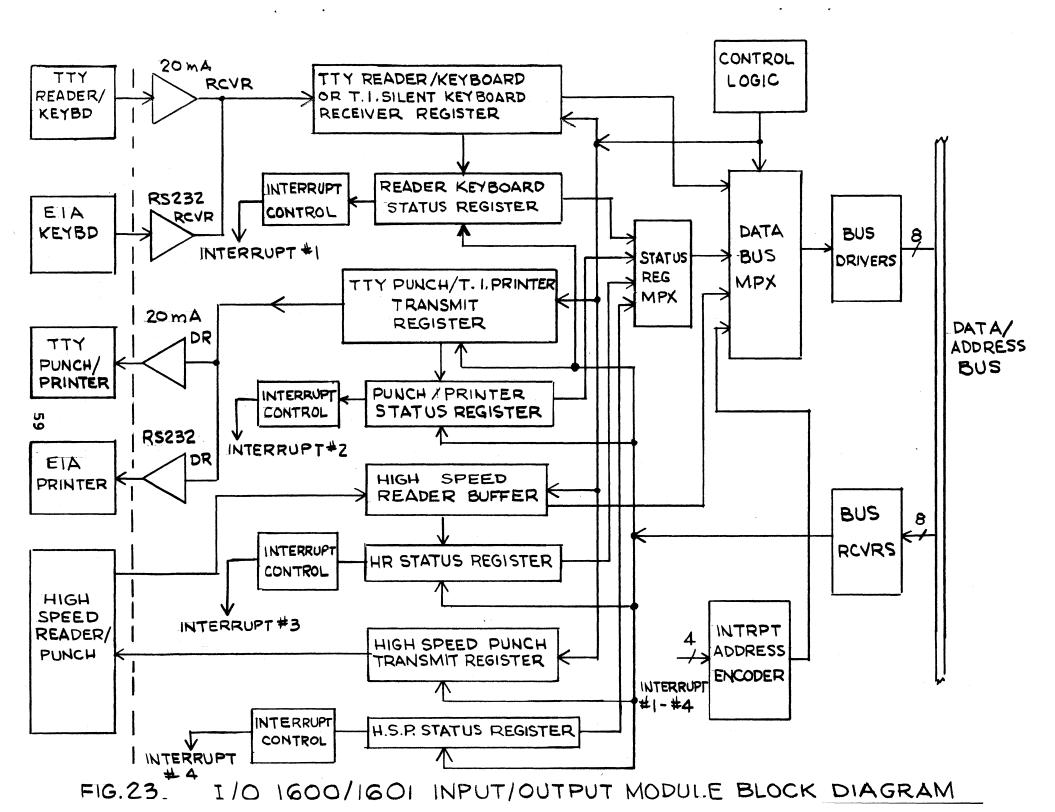

The basic GIC1600 Series Microcomputer System supports both Teletype and high speed paper tape reader/punch peripheral devices. All necessary hardware is contained in the fully character-buffered controllers located on the I/O1600/1601 Input/Output Module and all necessary software drivers are contained within the ROM Resident Operating System.

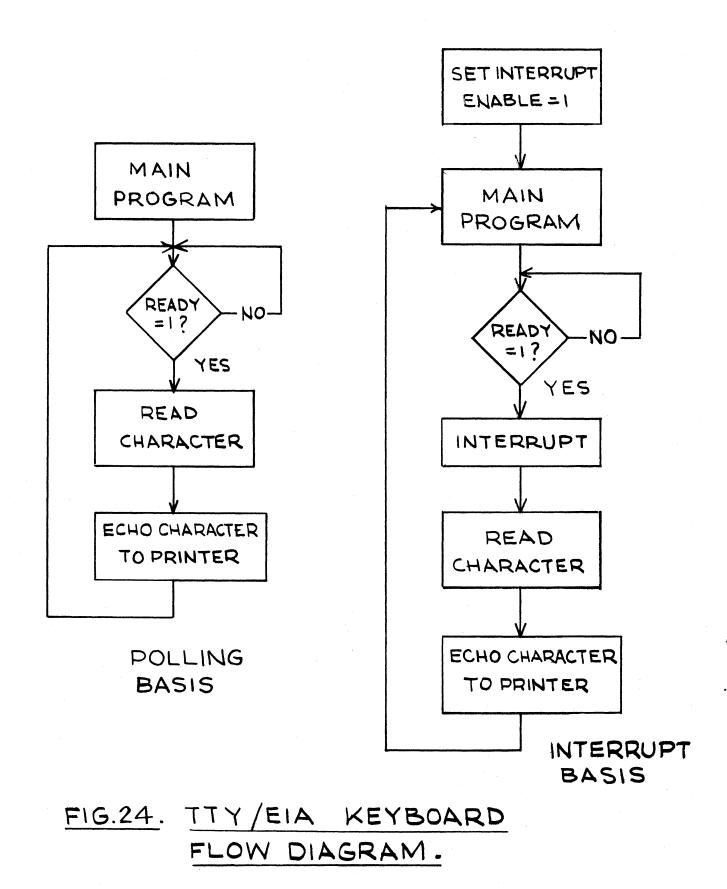

## 1.5.1 Teletype/EIA Devices

An ASR33 Teletype (Model ASR33, Catalog No. 3320/XXX with 20/60mA current loop) or any EIA compatible device can be used to provide interactive communication between the GIC1600 Series Microcomputers and the user. The TTY (or EIA device) can input data to the microcomputer via its keyboard or paper tape reader. The microcomputer can output information to the TTY (or EIA device) printer or paper tape punch.

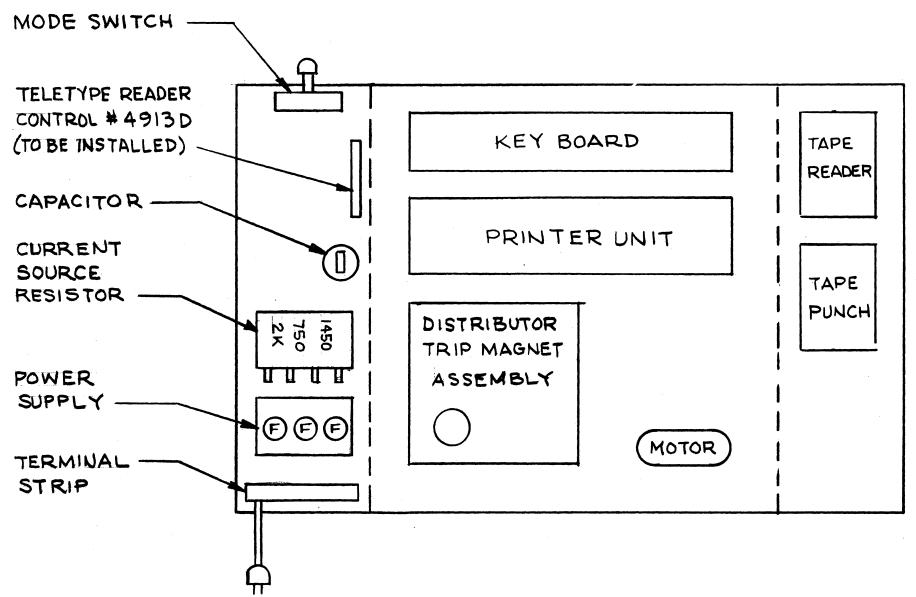

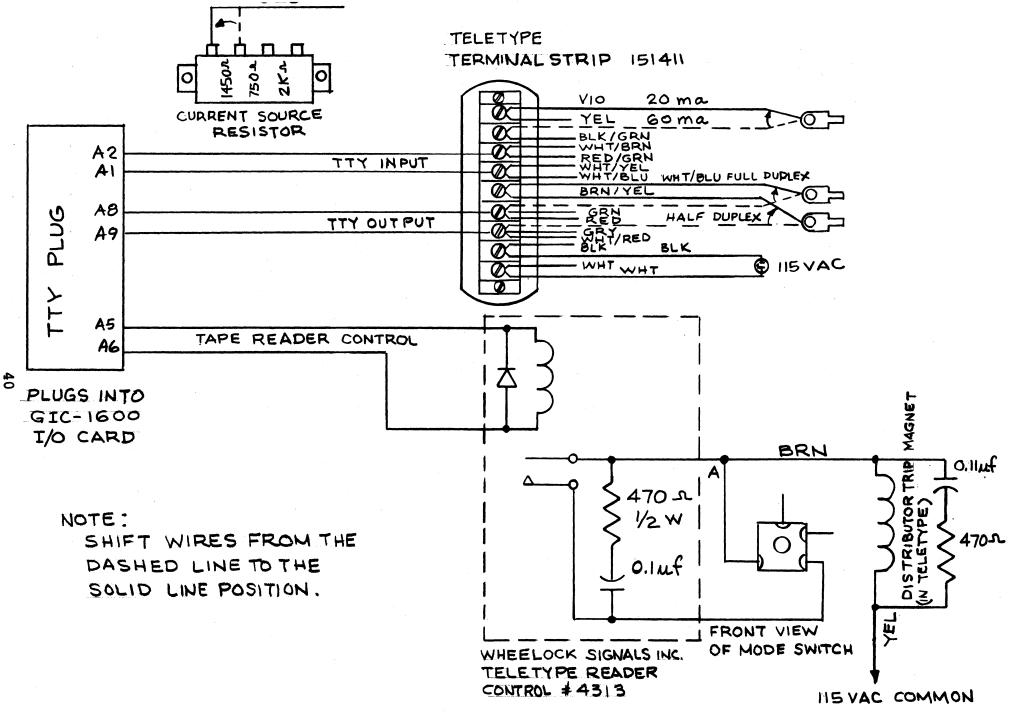

To use the Teletype with the GIC1600 Series Microcomputers, install the TTY cable plug into the smaller connector (10 pins) on the I/O1600/1601 Input/Output Module. The ASR33 Teletype must receive the follow-ing internal modifications and external connections (refer to Figures 17 and 18).

#### Internal Modifications

- 1. The current source resistor value must be changed to 1450 ohms. This is accomplished by moving a single wire.

- 2. A full duplex hook-up must be created internally. This is accomplished by moving two wires on a terminal strip.

# FIG. 17 . TOPVIEW - TELETYPE MODEL ASR33.

FIG. 18 . INTERFACE OF TELETYPE ASR33 AND GIC-1600 I/01600/1601 CARD.

- 3. The receiver current level must be changed from 60mA to 20mA. This is accomplished by moving a single wire.

- 4. A relay circuit must be introduced into the paper tape reader drive circuit if the TTY reader is to be used to asynchronously read tapes under program control. The recommended circuit consists of a relay, a resistor, a capacitor, and suitable mounting fixture. This relay network is manufactured by Wheelock Signals, Inc., as part "Teletype Reader Control #4913D". It may be mounted in the Teletype by using two tapped holes in the mounting plate shown in Figure 17 The relay network may then be added without alteration of the existing Teletype circuits. That is, Wire "A", to be connected to the brown wire in Figure 18, may be spliced into the brown wire near its connector plug. The "Line" and "Local" wires must then be connected to the mode switch. Existing reader control circuitry within the teletype need not be altered.

## External Connections

- 1. A two-wire receive loop, a two-wire send loop, and a two-wire tape reader control loop must be created. This is accomplished by the connection of six wires between the Teletype and the TTY Plug to the I/O1600/1601 card.

- 2. The TTY/EIA interface cable should have the following pin assignments:

| SIGNAL          | GIC1600                                  |

|-----------------|------------------------------------------|

|                 | (Upper Connector on I/O1600/1601 Module) |

|                 | (3M Connector #3473-0000)                |

| TTY PRINTER-    | A1                                       |

| TTY PRINTER+    | A2                                       |

| EIA SEND        | A3                                       |

| GND (EIA SEND)  | A4                                       |

| TTY RDR CONTROL | н A5                                     |

| TTY RDR CONTROL | - A6                                     |

| EIA RCVE        | A7                                       |

| TTY KYBD+       | A8                                       |

| TTY KYBD-       | A9                                       |

| GND (EIA RCVE)  | A10                                      |

|                 |                                          |

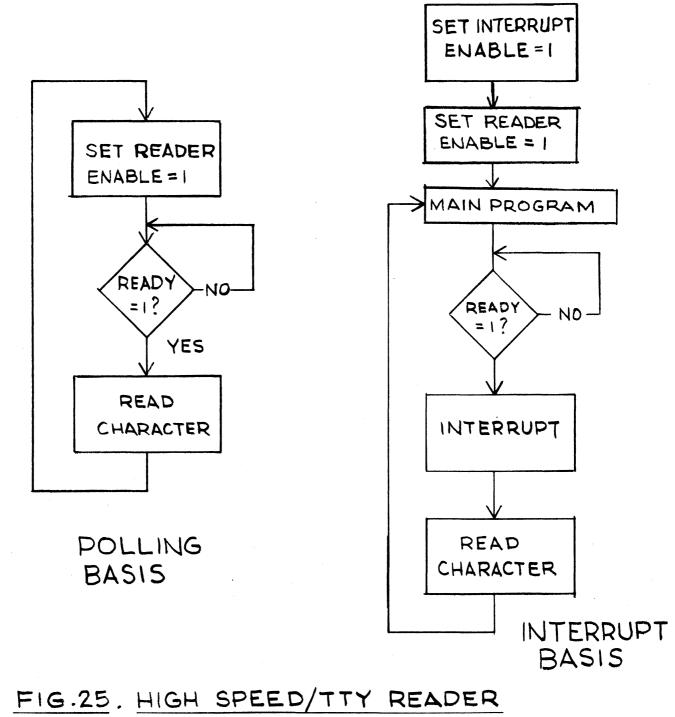

#### 1.5.2 High Speed Reader and Punch

A high-speed paper tape reader/punch can be a time-saving device during program preparation. The GIC1600 Series Microcomputer Systems can accommodate Remex (1733G Alton St., Santa Ana, Calif.) models RAB6375 and RAF6375 or equal. Tally (8301 So. 180th St., Kent, Washington) model 1315C is a plug-compatible equivalent. EECO (1441 E. Chestnut St., Santa Ana, Calif.) models RP-9360 and RPF9360 are equivalents in performance, but be sure to specify plugcompatibility with Remex 6375 series when ordering. For detailed reader/punch description and operating procedures, refer to the manual of the specific high-speed reader/punch being used.

GIC1600 Remex Remex Lower Connector on Punch (P1) Reader (P2) I/O1600/1601 Module (Cannon (Cannon (3M Connector #3414-3000) BD25P DB24S) Signal HSP 0 B1 1 HSP 1 B2 2 3 HSP 2 B3 HSP 3 B4 4 HSP 4 B5 5 B6 6 HSP 5 7 HSP 6 B7 B8 8 HSP 7 B9 GND 18 PUNCH COMMAND B10 11 25 GND B11 DIRECTION 10 B12 PUNCH INPUT --B13 14 MODE SELECT PUNCH OUTPUT --15 MODE SELECT B14 TAPE/CHAD ERROR B15 20 TAPE LOW B16 21 SYSTEM READY 13 B17 23 GND B18 PUNCH READY B19 12 -GND B20 -11 9 HSR DATA RDY B21 GND 13 B22 14 HSR READY B**2**3 -DRIVE LEFT B24 17 B25 1 HSR0 HSR MODE SELECT B26 10 2 HSR 1 B27 3 HSR 2 B28 HSR 3 B29 4 5 HSR 4 B30 6 B31 HSR 5 24 B32 GND 7 B33 HSR 6 **B34** 8 HSR 7

The interface cables should be less than 10 feet in length and should have the following pin assignments:

#### 1.6 SYSTEM MODULES

The GIC1600 Series Microcomputer Systems are built from a family of stand-alone, functional computer modules. All of these printed circuit cards are backplane compatible and can be combined in various combinations to suit individual customer requirements. At present the GIC1600 Series Modules include the following:

#### 1.6.1 Microcomputer Card

The Microcomputer Card contains the CP1600 Microprocessor and all the basic elements that are necessary for implementing a microcomputer system. It is packaged on a  $9.75'' \ge 9.25'' \ge .062''$  printed circuit board with a 140 pin connector for mounting into the card cage.

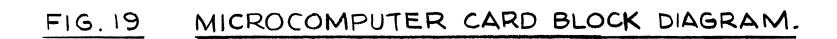

The major functional units on the card are shown in Figure 19 and are composed of the following:

- 1) CP1600 Microprocessor

- 2) 10 MHz Crystal Oscillator

- 3) Clock Generator

- 4) External Branch Multiplexer

- 5) Data Bus Driver/Receiver

- 6) Address Register/Address Bus Control Logic

- 7) Control Bus Decoder/Driver

- 8) Real Time Clock (Optional)

- 9) Power Fail (Optional)

- 10) Initialization Address Selection Logic

The following description details the logic and operation of the MC1600/ 1601 Card with reference to Schematic Dwg. No. DS-MC-002.

<u>CP1600 Microprocessor</u> - This chip is the Central Processing Unit for the GIC1600 Series Microcomputer Systems. It is described in detail in the CP1600 Microprocessor User's Manual.

Oscillator - The card contains an 8 MHz crystal oscillator (Y1 & U2-8, 9, 12, 13) that may or may not be used. The output (OSC) is provided at the connector. In order to use the oscillator a jumper is inserted between J22 (MCLK) and J57 (OSC) on the backplane of the Microcomputer.

<u>Clock Generator</u> - The clock generator circuitry divides the oscillator frequency (MCLK) into the high level, high speed, non-overlapping two phase clocks that are necessary for proper CPU operation. In addition, timing clock CK4\* is provided for the user. This signal corresponds to an internal CPU time slot (TS4) where most Data Bus and Control signal clocking is performed.

U19 is a 4-bit parallel-access, presettable shift register. Initially, a

DATA

DISBAR

BUSAK

0111 pattern is loaded while MCLR\* remains at its active low level. When MCLR\* is high, the 0111 pattern is continuously recirculated in the shift register by the MCLK signal since the output of the last flipflop is connected to the input of the first stage. CK1\* and CK3\* are ORed together via U11-3, 4, 5, 6 and buffered via U8-2, 7 to provide 01 for the CP1600. 02 is formed in a similar manner. U11 is crosscoupled to prevent both 01 and 02 from being high at the same time.

The card input, MCLR\*, must be held low momentraily after the power supplies are stable. In the GIC1600 Systems, the MCLR push button on the Control Console would be depressed after the power supplies have been turned on. U22, 1-6, synchronizes the positive transition of MSYNC\* with the falling edge of CK3\*; this is needed to synchronize the CP1600 with the clock.

External Branch Multiplexer - In order to provide external branching capability, a sixteen to one multiplexer (U14) is supplied on this board. Each of the external branch conditions (EBC0-15\*) is "0" active so that a true condition is sensed by a logical "0". The BEXT instructions per-form the branch when the external branch inputs (EBC0-15\*) are logic "0".

Data Bus Driver/Receiver - A 16-bit high speed driver/receiver comprised of U1, U3, U7 and U10 is provided to buffer each of the 16-data lines of the CPU. The output of the driver is the Data Bus which is connected to the memory and all the peripheral by U15. During CK1\* both inputs to latch U15, 1-6, are held high. On the rising edge of CK1\*, pin 1 will be set low if BDIR from the CPU is high, causing the latch output to latch high (CPU data to be transferred to the bus).

Address Register/Address Bus Control Logic - A sixteen bit wide address register (U18, U21, U25 and U29) is supplied on this card along with an output driver (U13, U17, U20 and U24). This register is clocked during CK4\* if ADAR\*, BAR\* or INTAK\* is decoded by U26. Access to the Address Bus for DMA operation is provided. A logical "0" input applied to DISBAR\* will floate the address bus via U28, 10-11 and U22, 11-13 as long as the CPU has acknowledged BUSRQ\* with BUSAK\*.

A MAXADR\* input is also supplied, but it is used exclusively by the control console card to force the storage of the current program counter into address 177777 for TRAP interrupt instructions associated with the On Line Debug Program (S160DP) which is part of the Resident Operating System.

Bus Control Decoder/Driver - CPU control lines BC1, BC2 and BDIR are decoded by U26 to provide the Control Bus signals. Each output control line of the decoder has an open collector output so that DMA control can be achieved by wire "OR"ing. As the decoder is enabled by CK1\* the Control Bus is valid only during CK2, CK3 and CK4. <u>Real Time Clock</u> - The Real Time Clock option interrupts the CPU and supplies a starting address to the bus at specified intervals of time. U30 is a timer whose period can be set by user-selected components, RA, RB and CT. U27 syncs the RTC interrupt request with the CPU.

Initially, the Interrupt Acknowledge (IACK) FF (U16) is "0". This allows an INTR\* (Interrupt Request Not) via U9, 4-6, if there is a RTC or Power Fail (PF) interrupt request. The IACK FF is preset if either the RTC or the Power Fail (PF) is requesting an interrupt (U12, 1-3) and the INTAK\* (Interrupt Acknolwedge Not) pulse comes from the Bus Control Logic (U9, 1-3) in response to the INTR\*. INTR\* is then raised high as soon as IACK is preset, again via U9, 4-6.

During the NACT\* time, which follows the INTAK\* in an interrupt sequence, (see the CP1600 Microprocessor User's Manual) the RTCRQ FF (U27, 8-13) will be set to "0". The IACK FF enables U6, 11-13, which ultimately allows the starting address of the RTC interrupt routine (RTCSTAD\*) to be placed on the bus. The IAB\* pulse which appears in an interrupt sequence gates the address onto the bus via U9, 11-13 and also clears U27, 1-6 via U12, 4-6, and U6, 8-10, to allow future interrupts. The TCI (Term-inate Current Interrupt) software command will cause the CPU to generate a TCI signal on pin 26 of the CP1600, which will clear the IACK FF at the end of the RTC interrupt routine.

<u>Power Fail Option</u> - The Power Fail Option enables the user to save critical register information if he has either a core memory or a semiconductor RAM memory with battery backup. The Power Fail Sense Signal In (PFIN\*) is synchronized to the CPU by being clocked into U16, 8-13 by the next available NACT\* signal. As with the RTC above, PFRQ generates INTR\*. When the IACK is preset, PFSTAD\* (Power Fail Starting Address) is allowed onto the bus during IAB.

If the Real Time Clock Option or the Power Fail Option is not used, IPRO\* (Interrupt Priority Out Not) is strapped to INTAK\* (S1 to BO), so that INTAK\* is enabled for the next card down the priority chain. U28-1 is strapped to PB which is +5 volts or the Power Fail Option is used, IPRO\* is strapped to pin 8 of U12 (S1 to B1) and U28-1 is strapped to U16-6 (S0 to A1). Gate U12, 8-10, prevents the INTAK\* pulse from acknowledging an interrupt further down the priority chain if RTC or PF requests an interrupt. Strap S0 to A1 is needed to mask out further interrupts down the priority chain while the IACK FF is set to a "1".

Gate U6, 1-3, decides in favor of the Power Fail if the Power Fail requests an interrupt within the time an interrupt is requested by the RTC and the IAB pulse presents the interrupt address to the bus.

Initialization Address Selection Logic - Two signals, STAD0\*-1\*, are

provided by the Microcomputer Card for generating the starting address of the user's Interrupt Branch Table. The user may tie on the backplane either or both of these lines to Data Bus lines to eliminate the need for extra open collector drivers. For example, if the main program begins at address 030000: DBL12\*, 13\*, should be tied to STAD0\*, 1\*, respectively. They are gated (U5, 1-6) by DISTAD\* (Disable Starting Address Not). DISTAD\* is provided for use by the Control Console Card. The Control Console Card lowers DISTAD\* when it interrupts the CPU, so that the program counter is forced to an address specified by the Control Console Card during IAB rather than the one specified by the user on the CPU card. On startup, for example, the Control Console Card would place the entry address of the Resident Operating System on the bus and lower DISTAD\* to the CPU card; thereby causing the GIC1600 Systems to always start by typing S16ODP V01A.

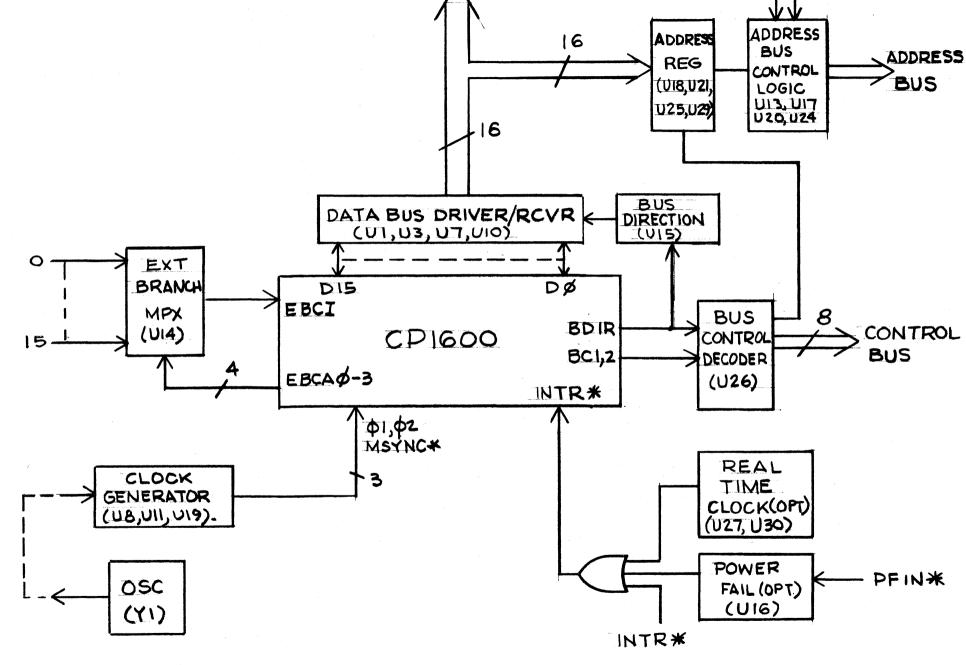

## 1.6.2 2K Memory Card

The 2K x 16 Memory Card provides the GIC1600 Systems with a 2K x 16bit static random access memory (RAM). There are thrity-two 22 pin 256 x 4 static RAMs packaged on a 9.75" x 9.25" x .062" printed circuit board with a 140 pin I/O connector. These RAMs are TTL compatible and operate from a single +5 volt supply. Read access and write cycle times for the card are each specified as 550nsec maximum for all rated variations in power supply over the 0°C to 55°C temperature range.

The 2K x 16 Memory Card is shown in block diagram from in Figure 20. The major functional units on the card are:

- 1) Memory Matrix

- 2) Row Decoder

- 3) Card Decoder

- 4) Bus Control Logic

- 5) Read/Write Logic

The following description details the logic and operation of the RM1600 card with reference to Schematic Dwg. No. S-RM-012.

<u>Memory Matrix</u> - The static memory is organized as 2048 rows of 16 bits each. Each horizontal grouping of four RAM's (main row) contains 256 of the rows. Each of the four RAM's in a horizontal grouping (main row) contributes 4 of the 16 outputs. Addresses 0-7 (BADR0\* - BADR7\*) are applied to each group of 256 rows via U29 and U30.

Main Row Decoder - The desired horizontal group of four RAM's (main row) is selected by enabling the chip select inputs on the four RAM's via the 3-to-8 decoder U24.

Card Decoder - U35 and U40 decide if this is the particular memory card

\_\_\_\_\_

out of a number of memory cards that needs to be addressed. The output of U40 enables the row decoder (U24) and the output data bus control logic. The user is provided with four backplane pins HW1-4 on each general purpose slot that may be wired to either Vo (J41) or to AND. For example if the beginning address is 20000 HW3 should be tied to Vo while HW1, 2, 4 should be tied to gnd. For systems using 4-2K boards the backplane is wired for the lowest 8K (i.e., '0-'17777). Note that the standard memory module is strapped for the lower 32K, alt hough the card can be modified for the higher 32K by strapping So to U and removing the jumper between So and L on the card.

Bus Control Logic - If the card is to be accessed, U46-6 enables U47-1 and U47-3. Higher and/or lower byte selection is done via U45, 8-13, enabling U47-2 and U47-4. If the MC1600 Microprocessor Card outputs a DTB\* or an ADAR\* signal requesting the use of the memory, U46-8 presents a pulse to U47-5 and U47-13. If the higher byte is selected, U13 and U19 then present DBL8\*-DBL15\* to the Data Bus. If the lower byte is selected, U2 and U3 then present DBL0\*-DBL7\* to the Data Bus.

<u>Read/Write Logic</u> - When the write command DWS\* is presented from the MC1600 Microprocessor Card, U45, 1-6, select whether the higher or lower byte of a given 16-bit word is written into the memory.

Note: The basic MC1600/1601 Microcomputer Module does not use the byte select feature of the RM1600 Memory Module.

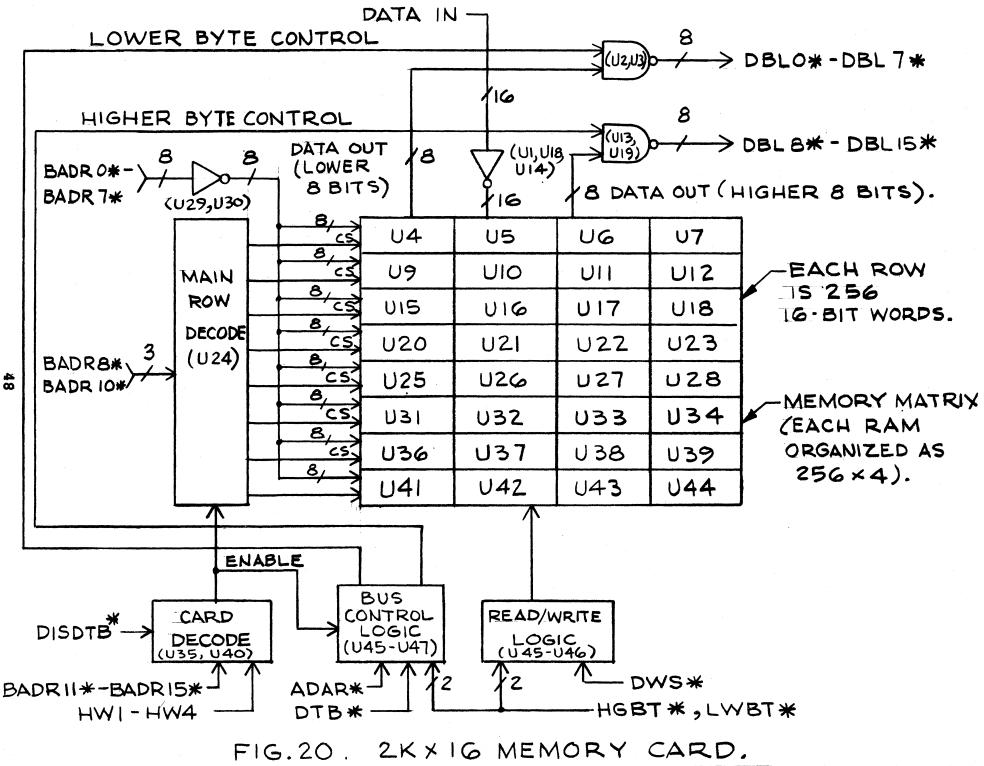

#### 1.6.3 8K Memory Card

The 8K x 16 Memory Card provides the GIC1600 Systems with an 8K x 16-bit RAM for program and data storage. There are thirty-two 22-pin 4096 x 1 RAM's packaged on a 9.75" x 9.25" x .062" printed circuit board with a 140 pin I/O connector. As with the 2K x 16 Memory Card, read access and write cycle times for the card are each specified as 550nsec maximum for all rated variations in the power supplies over the 0°C to 55°C temperature range.

The 8K x 16 Memory Card is shown in block diagram form in Figure 21. The major functional units on the card are:

- 1) Memory Matrix

- 2) Main Row Decoder

- 3) Card Decoder

- 4) Bus Control Logic

- 5) Read/Write Logic

- 6) DC-to-DC Converter

The following description details of function and operation of the RM1601

FIG. 21. BKX16 MEMORY CARD.

Memory Module:

<u>Memory Matrix</u> - The memory is organized as  $819^2$  rows of 16 bits each. Each of the two main rows (horizontal groupings of 16 RAMs) contain 4096 of the rows. Each of the 16 RAMs in a main row contributes 1 of the 16 outputs. Addresses 0-11 (BADR0\* - BADR11\*) are applied to each group of 4096 rows.

<u>Main Row Decoder</u> - The desired horizontal grouping of 16 RAMs (main row) is selected by enabling the chip select inputs on the 16 RAMs. BADR12\* is steered via LWBT\* and HGBT\* (as on the 2K x 16 Memory card) to two chip select drivers for the top row and BADR12 is steered via LWBT\* and HGBT\* to two chip select drivers for the bottom row.

<u>Card Decoder</u> - The card is selected via gating similar to the RM1600  $2K \ge 16$  Memory Card. HW1-3 are provided to select the particular 8K memory address block that the module will occupy. For example, if the beginning address is 20000, HW1 should be tied to Vo while HW2 & 3 should be tied to GND. For systems using 1-8K module the backplane is wired for the lowest 8K in slot 3.

<u>Bus Control Logic</u> - The bus is driven via logic similar to the RM1600  $2K \ge 16$  Memory Card discussed above.

<u>Read/Write Logic</u> - In addition to providing the read/write controls to the RAMs, this logic provides a NACT \* signal to latch the output data after a read operation since the output data is valid only for a certain amount of time after the chip select signal falls.

<u>DC-to-DC Converter</u> - A 12 volt to 15 volt converter is required to power the chip select drivers.

## 1.6.4 Control Console Card

The Control Console Card provides the interface between the Control Panel and the CP1600 Microprocessor. It is packaged on a  $9.75'' \ge 9.25'' \ge .062''$  printed circuit board and a 140 pin connector is located on the edge of the card for mounting into the card cage supplied. Connection to the control panel is achieved with two flex cables and are connected to another edgeboard connector mounted on the Control Console Card.

Thie card contains control logic to handle all front panel commands as well as the required interrupt logic to interface with the CPU. The basic functional units on the card are shown in Figure 22 and consist of the following:

- 1) Data Multiplexer and Data Bus Driver

- 2) Switch Register

- 3) Status Register

CONTROL CONSOLE CARD AND PANEL BLOCK DIAGRAM. FIG. 22.

.

1

- 4) Address Multiplexer

- 5) Control ROMs (Resident Operating System)

- 6) Scratchpad memory (RAM)

- 7) Control Panel Logic

- 8) Interrupt Logic

The following description details the function and operation of the CC1600 Control Module with reference to Schematic Dwg. No. DS-CC-007.

#### Data Multiplexer and DAta Bus Driver, Switch Register and Status Register

The data multiplexer comprised of U24, U23, U19, U18, U14, U13, U4 and U3 enables data to be placed on the data bus as a function of its two control lines, A and B:

| A | В | DATA                                                                                                 |

|---|---|------------------------------------------------------------------------------------------------------|

| 0 | 0 | ROM/RAM Output                                                                                       |

| 0 | 1 | Switch Register Data                                                                                 |

| 1 | 0 | Status Register Data                                                                                 |

| 1 | 1 | ROM/RAM Output<br>Switch Register Data<br>Status Register Data<br>Interrupt Address (170000 for ODP) |

#### A=B=1:

When the Master Clear Switch (MCLR\*) is depressed after power is applied, MAXADR\* at U48-8 goes low. This, in turn, presets U44, 8-13 to a "1", forcing the multiplexer control signals (A at U33-11 and B at U33-3) to a "1". The Interrupt Address for the Resident Operating System (170000) will now be presented to the inputs of the data bus drivers U29, U28, U9 and U8.

The first control signal from the CP1600 after MSYNC\* goes high is an Interrupt Address to Bus (IAB\*). (See Sec. 2.3 of the CP1600 Microprocessor User's Manual). IAB\* is buffered by U48, 1-3. It then passes thru the Bus Control OR gate U52, 1-6, and allows the Interrupt Address onto the bus by gating on the data bus drivers. During the NACT time that follows the IAB on the Bus Control lines, the Interrupt address is stored in R7 (the Program Counter) in the CP1600. Then the CP1600 outputs the Program Counter to the Bus Address Register on the MC1600 card and the On-Line Debug Program begins. (Part of Resident Operating System). ODP clears its pseudo-registers located in the ODP RAM (see Figure 2 - Memory Map).

A=B=0:

If data from the output of the 16-bit RAM comprised of U2, U7, U17 and U22 or one of the 10-bit On-Line Debug ROMs comprised of U27, U37, U42, U47, U56 and U62 (the higher six bits are tied to a "1") are to be placed on the data bus, the control signals A and B must be "0". A and

B being low is the normal quiesient state of the multiplexer; if the switch register, the status register or the interrupt is not requesting service by the user, A and B will be "0". Logically, to have U33-3 and 11 low, U33-1, 2, 12, 13 must be high. U33-2 and 12 are high since U44, 8-13 will not be set. U33-1 and 13 will be high since address 177 XXX (which is required by the switch or status registers being steered thru the multiplexer) has not been decoded at U38-9. The "1" at U38-9 is ORed thru U43, 4-6, U-43, 11-13 and U43, 8-10 and presented to U33-1 and 13. Thus, the multiplexer will be steering RAM/ROM data in the data bus drivers unless otherwise directed.

#### A=1; B=0:

The switch register of the control panel is used for data and address entry. It can be inspected by the CP1600 by a MVI 177200, R0 type instruction. When the first four high order bits appear as 1's on the address register, U58-2 goes low enabling U38, U38-9, in turn, will go low for the first seven high order bits being 1. U43-6 will then go low for 1 111 111 0XX XXX XXX. If BADR7 is high, B will be one and A will be zero. (The Interrupt Address FF, U44, 8-13, is not set and both U33, 1-3 and U33, 11-13 are low. Note all addresses between 177200 and 177377 will decode in an identical manner and thus all are reserved for the switch register). With A=1 and B=0, the multiplexer gates SWR0 thru SWR15 onto the data bus.

A=0, B=1:

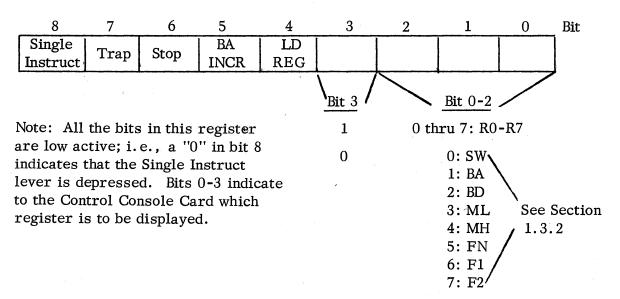

The status register of the Control Console Panel is defined below:

This status register can be inspected by the CP1600 by a MVI 177000, R0 type instruction. The decoding is the same as described above for the switch register, except that A will be zero and B will be one, since BADR7 is now 0 and not 1. (Note again that all addresses between 177000 and 177177 will decode in an identical manner and thus all are reserved for

the status register). U15 encodes the 8 register lines to 3 bits. With A=0 and B=1, the multiplexer gates the status register onto the bus.

The data multiplexer is enabled for the ROM/RAM, the switch register and the status register since they all require 17XXXX to be decoded which is done by U52, 8-13. Presenting the Interrupt Address to the data bus also requires 17XXXX to be decoded; MAXADR\* created by the interrupt places 177777 on the bus. Thus, the data multiplexer is enabled for all four uses.

U40, U45 and U50 drive the data display lamps in the Control Console Panel. U52, 1-6, serves as an OR gate to allow DTB\*, IAB\* and ADAR\* to strobe the multiplexed data onto the bus through gates U8, U9, U28 and U29 when commanded by the CP1600.

#### ADDRESS MULTIPLEXER

Multiplexer U36, U41, U46 and U51 directs the Bus Address Register onto the Control Console Card in the Run mode (if the machine is not in the Single Instruct mode). In the Halt mode, the multiplexer places all 1's onto the card, except for the least four significant bits, which are the encoded register lines that are used as addresses to display the top 16 locations of the RAM contents. When halted, the contents of the R0 to R7 registers and the contents of the SW, BA, BD, ML, MH, FN, F1 and F2 registers can thus be displayed. The Halt signal forces 1's on multiplexer U51's output. U52, 8-13, decode these 1's to a 0, which enables the data multiplexer. If the Control Panel is not disabled by DISCC\* (Disable Control Console Not), the high level of the Halt signal on U61-2 passes to U52-6, which enables the data bus drivers and thus allows the RAM contents to be displayed during halt, if selected.

In the Single Instruction mode, an interruptable instruction is placed on the data bus in place of certain non-interruptable instructions. When this occurs, DISDTB\* at U21-10 goes low forcing U51-1 high, which places 0's on all the outputs of U51. This disables the data multiplexers and forces all their outputs low. When DTB enables the data bus drivers, the data multiplexer will not contribute any data to the bus, thereby freeing the bus for the NOP instruction needed for the Single Instruction mode.

#### CONTROL ROMs

The firmware necessary for the Resident Operating System and the On-Line Debug Program is incorporated in ROMs U27, U37, U42, U47, U56 and U62. They are all supplied with input addresses BADR0-8; each chip is selected by decoder U38 using BADR9-11. The ROM outputs are routed thru the data multiplexer as discussed above.

#### SCRATCHPAD MEMORY (RAMs)

The top 16 locations of the Scratchpad Memory formed by RAMs, U2, U7, U17 and U22 store the R0 to 7 registers and the SW, EA, BD, ML, MH, FN, F1 and F2 registers as shown in the Memory Map in Figure 2. The other 240 locations are used for temporary storage for the On-Line Debug Program. The RAMs are all supplied with input addresses BADR0-7; all chips are selected by addresses BADR8-11 being all 1's via U63, 8-10. The RAM outputs are routed thru the data multiplexer as discussed above.

#### CONTROL PANEL LOGIC

The Control Panel Logic in conjunction with the On-Line Debug Program enable the user to inspect and modify CPU registers, memory locations and I/O device registers, and to read and punch paper tapes.

When the CPU is halted, the control panel is enabled by U50, 3-4. U30 debounces and latches LDREG, BA INCR, START/STOP and PCINH. If LDREG or BAINC is depressed when the machine is halted, an interrupt request is sent to the CPU via U34 and U57, 11-13. The CPU is also started in a delayed fashion via U25, 1-6 and delay inverters U32, 12-13 and U12, 1-4 so that the interrupt request is present at the CPU when the start command is given. The appropriate routine is then selected and executed under control of the ODP program. The machine is then halted.

If the START/STOP switch is depressed and the machine is halted, the negative transition on U32-8 will cause a negative transition on U39-8. This will be ORed through U25, 1-6 causing the machine to start. After the machine is started, the HALT signal on U53-13 will go low, resetting the STRT FF, U39, 8-13.