**PRICE \$8.00**

.

-

1

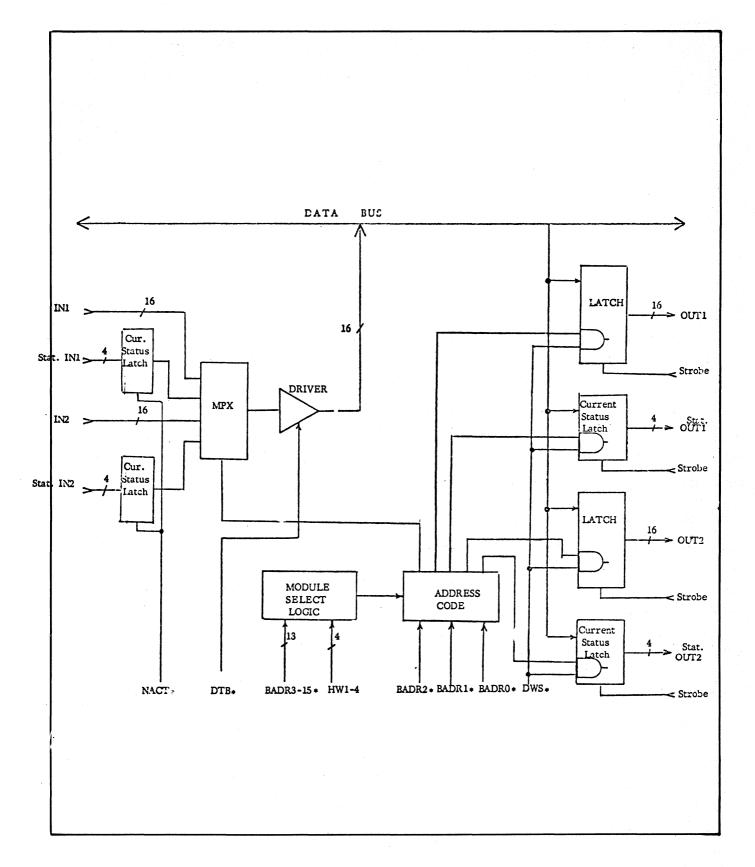

# SERIES 1600 MICROPROCESSOR SYSTEM

GENERAL INSTRUMENT MICROELECTRONICS

# SEMICONDUCTOR DOCUMENTATION

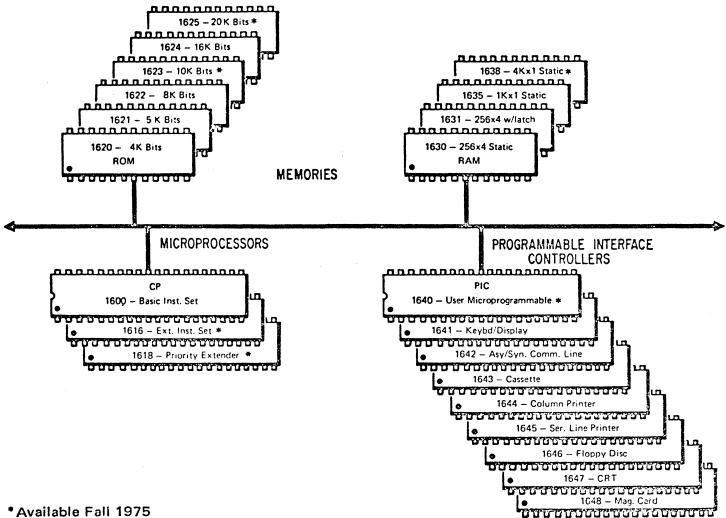

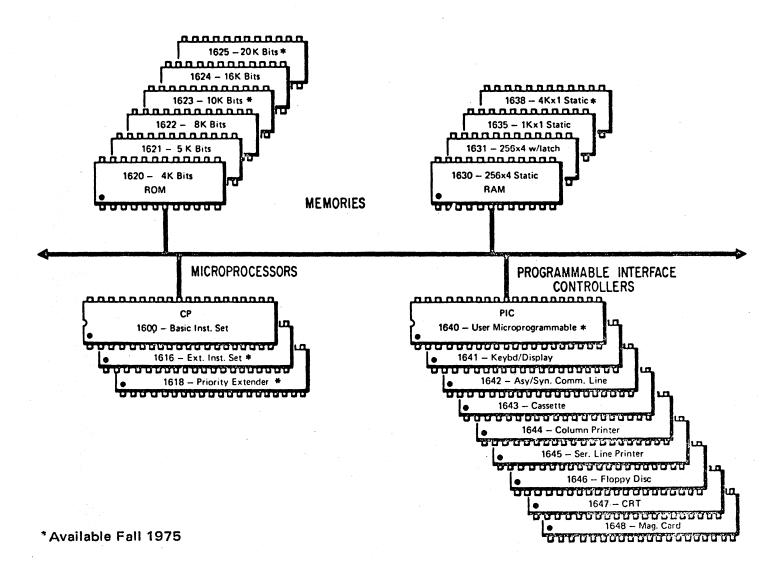

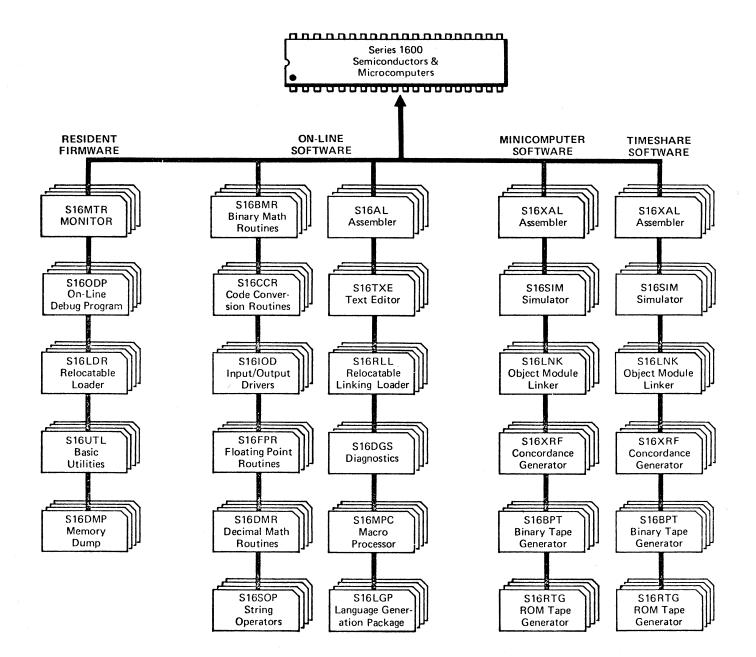

#### THE SERIES 1600 SEMICONDUCTOR LINEUP

\* Available Fall 1975

# SERIES 1600 MICROPROCESSOR SYSTEM SEMICONDUCTOR DOCUMENTATION

CP-1600 MICROPROCESSOR USERS MANUAL

This manual contains a detailed specification of the CP-1600 microprocessor array including theory of operation, electrical parameters, instruction set, and some typical applications examples.

C Copyright 1975 All rights reserved

# SUMMARY

| Title:          | CP1600 Microprocessor Users Manual                                                                                                                                                                                                                                                                                                                                  |  |

|-----------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| Document No.:   | S16DOC-CP1600-04, May 1975                                                                                                                                                                                                                                                                                                                                          |  |

| Revision Level: | Supersedes S16DOC-CP1600-03, March 1975                                                                                                                                                                                                                                                                                                                             |  |

| Scope:          | This manual describes the CP 1600 microprocessor array.<br>It includes information on the theory of operation of the<br>processor, timing diagrams of all operational sequences,<br>electrical parameters, and details of the instruction set.<br>In addition, a number of systems configurations of the<br>CP 1600 are shown by way of typical interface examples. |  |

Reference Documents:

S16DOC-GIC1600-00 S16DOC-XALSIM-01 GIC1600 Microcomputer Users Manual Series 1600 Cross Software Manual

### TABLE OF CONTENTS

CHAPTER 1 - GENERAL DESCRIPTION

1.0 INTRODUCTION

CHAPTER 2 - PROCESSOR SPECIFICATION

2.0 **PROCESSOR DESCRIPTION**

2.1 PROCESSOR SIGNALS

2.2 INTERNAL CPU ARCHITECTURE

2.2A Basic Functional Blocks

2.2B Processor Timing

2.2C Processor Sequences

2.3 TIMING DIAGRAMS

2.4 ELECTRICAL SPECIFICATIONS

CHAPTER 3 - INSTRUCTION SET

3.0 GENERAL INSTRUCTION FORMAT

3.1 INSTRUCTION DESCRIPTION

3.1.1 Symbolic Notation

3.1.2 Operation of Status Bits

3.1.3 Instruction List

3.2 EXTERNAL REFERENCE INSTRUCTIONS

3.2.1 Data Access Instructions

3.2.2 Conditional Branch Instructions

3.3.3 External Reference Addressing Modes

3.3 INTERNAL REFERENCE INSTRUCTIONS

3.3.1 Register to Register

3.3.2 Register Shift

3.3.3 Single Register

3.3.4 Internal Control

3.3.5 Jump/Jump and Save Return

# TABLE OF CONTENTS

#### (Continuation)

# 3.4 PROGRAM EXAMPLES

- 3.4.1 Loop or Iteration Control

- 3.4.2 Table Access

- 3.4.3 Transfer via Dispatch Table

- 3.4.4 Evaluate Variables

- 3.4.5 Arithmetic Operations

- 3.4.6 Stack Operations

- 3.4.7 Interrupt Processing

- 3.4.8 Subroutines

- 3.4.9 BEXT Instruction

- 3.4.10 Code Conversion Examples

CHAPTER 4 - SYSTEM CONFIGURATIONS

- 4.0 BASIC IMPLEMENTATION

- 4.1 BUS STRUCTURE

- 4.2 CLOCKS

- 4.3 EXTERNAL SENSE LOGIC

- 4.4 START/STOP HALT FUNCTIONS

- 4.5 INTERRUPT SYSTEM

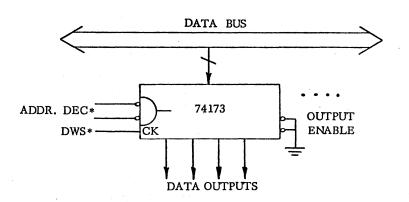

- 4.6 BASIC INPUT/OUTPUT PORTS

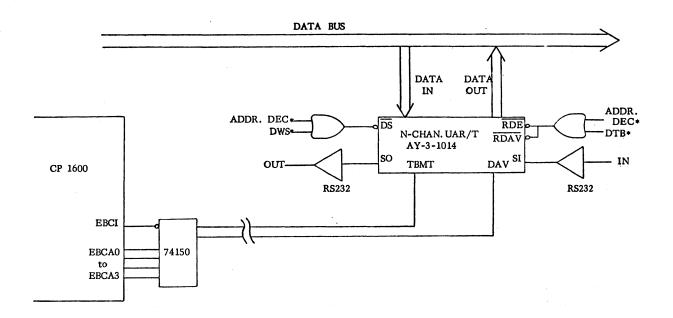

- 4.7 SIMPLE COMMUNICATION INTERFACE

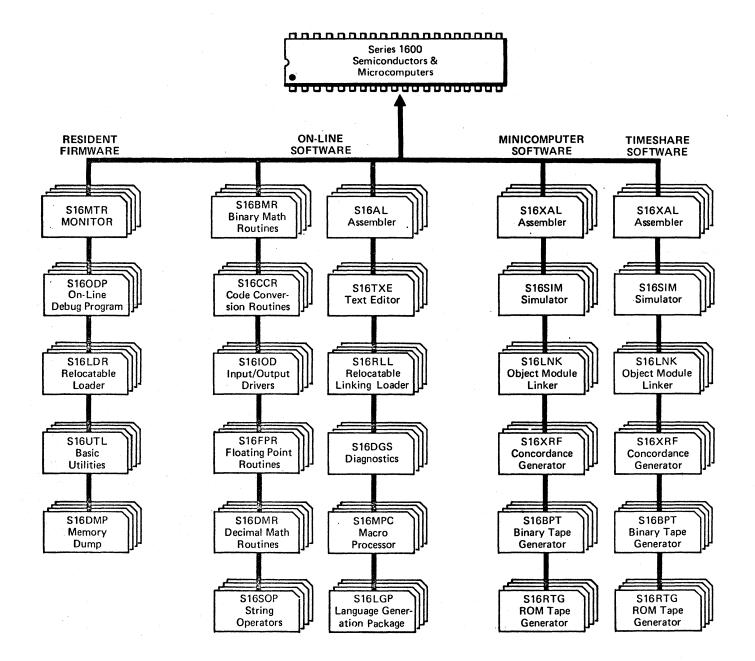

# APPENDIX - SERIES 1600 MICROPROCESSOR PRODUCTS SEMICONDUCTOR COMPONENTS SOFTWARE MICROCOMPUTER HARDWARE

#### CHAPTER 1

#### CP1600 GENERAL DESCRIPTION

#### 1.0 INTRODUCTION

The CP1600 MicroProcessor Unit is a compatible member of the Series 1600 MicroProcessor Products family. It is a complete, 16-bit, single chip, high speed MOS-LSI MicroProcessor. The Series 1600 is fabricated with General Instrument's N-Channel Ion-Implant GIANT II process, insuring high performance with proven reliability and production history. All members of the Series 1600 Family, including Programmable Interface Controllers, Read Only Memories, and Random Access Read/Write Memories, are fully compatible with the CP1600.

The CP1600 MicroProcessor Unit is designed for high speed data processing and real time applications. Using a 5 MHz, 2-phase clock, the CP1600 completes a microcycle in 400 nanoseconds. Typical applications include programmable calculator systems, peripheral controllers, process controllers, intelligent terminals and instruments, data acquisition and digital communication processors, numerical control systems, and many general purpose computer applications. The MicroProcessor can readily support a variety of peripheral equipment such as TTY, CRT display, tape reader/punch, A/D & D/A converter, keyboard, cassette tape, floppy disk, and RS-232C data communication lines.

The CP1600 MPU utilizes third generation minicomputer architecture with eight general purpose registers to achieve a versatile, sophisticated microcomputer system. The 16-word enables fast and efficient processing of alpha-numeric or byte oriented data. The 16-bit address capability permits accessing of 65, 536 words in any combination of program memory, data memory, or peripheral devices. This single address space concept, combined with a powerful instruction set and microprogrammable Peripheral Interface devices, provides an efficient solution to all microcomputer and many minicomputer-based product requirements.

- 87 BASIC INSTRUCTIONS

- · 16-BIT, TWO'S COMPLEMENT ARITHMETIC AND LOGIC OPERATIONS

- STATUS REGISTER OVERFLOW, CARRY, SIGN, ZERO, INTERRUPT ENABLE

- ARITHMETIC, LOGICAL, AND CIRCULAR SHIFTS

- 8 INTERNAL PROGRAM ACCESSIBLE GENERAL REGISTERS (16-BIT)

- MEMORY STACK POINTER/UNLIMITED STACK DEPTH

- IMMEDIATE DATA, DIRECT (65K), AND REGISTER INDIRECT (65K) ADDRESSING

- PROGRAM COUNTER RELATIVE ADDRESSING ON CONDITIONAL BRANCH

- · CONDITIONAL BRANCH STATUS REGISTER, AND 16 EXTERNALS

- TWO PROGRAMMABLE INTERRUPT LINES WITH PRIORITY RESOLUTION AND SELF IDENTIFYING ADDRESSES

- DMA CHANNELS FOR HIGH SPEED DEVICE TRANSFERS

- TTL COMPATIBLE/SIMPLE BUS STRUCTURE

- · CYCLE TIME: 400 NSECS

- · ADDS TWO 16-BIT INTERNAL REGISTERS IN 2.4 μSECS

- MEMORY TO REGISTER ADD TWO 16-BIT NUMBERS IN 3.2 μSECS

# CHAPTER 2

# CP 1600 PROCESSOR SPECIFICATION

## 2.0 PROCESSOR DESCRIPTION

The General Instrument Corporation CP 1600 microprocessor is a high speed, 16-bit machine featuring full 16-bit address/data transfer and a 400 hanosecond internal cycle time. Full instruction execution times range from 1.6 to 4.8 microseconds.

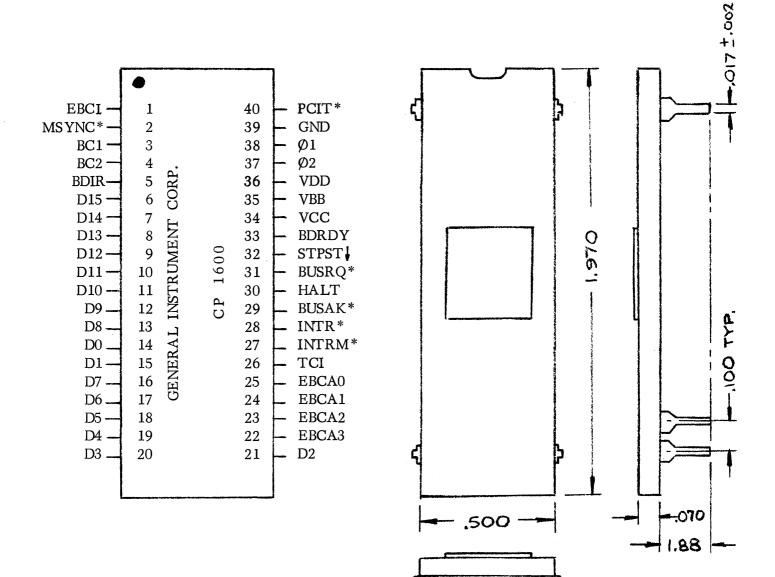

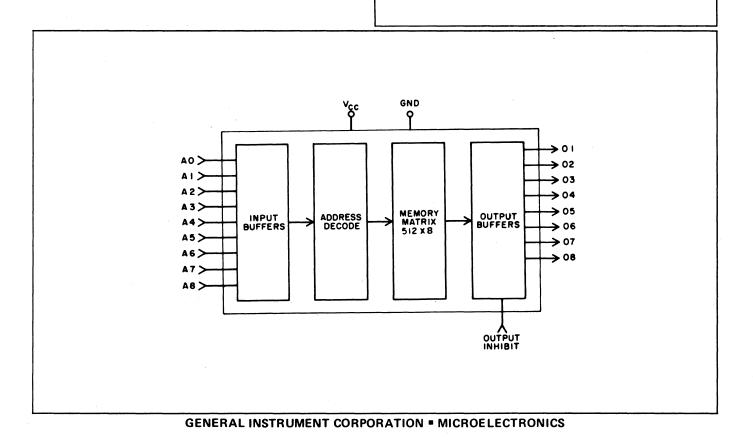

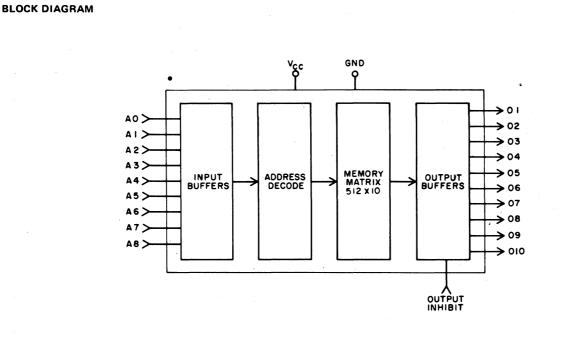

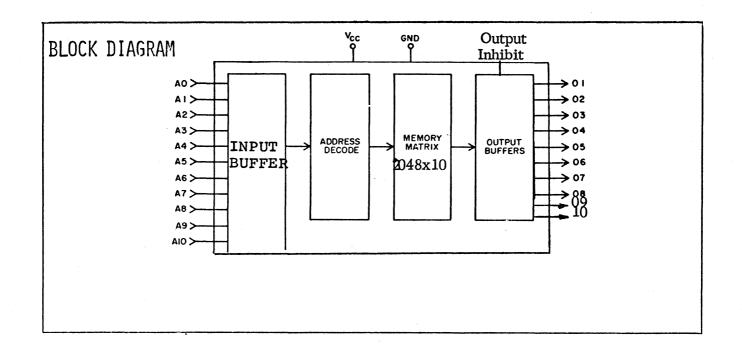

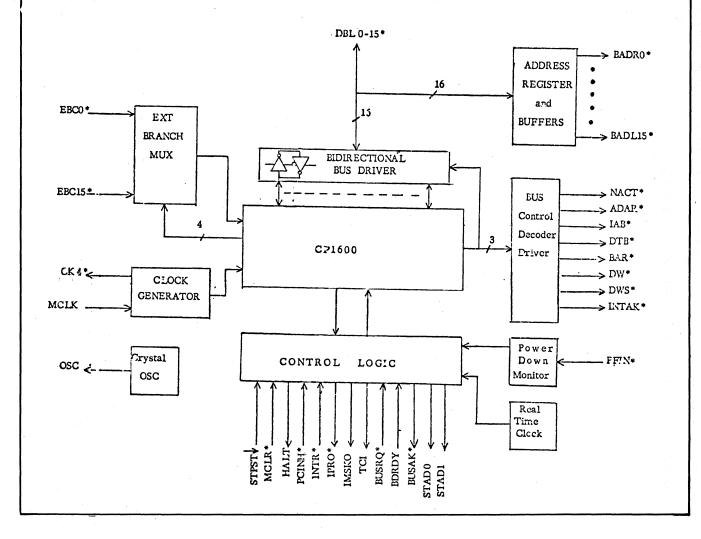

The processor contains 8 general purpose 16-bit program accessible registers, a high speed ALU, an instruction register and microcontrol unit, and TTL compatible input/output buffers. The CP 1600 is supplied in a 40 pin dual-in-line ceramic package with input/output signals shown in Fig. 2-1.

002

001

010

.600

#### Logic Conventions:

- \* Negative logic (low assertion)

- Low to high edge trigger

- High to low edge trigger

All others Positive logic (high assertion)

#### 2.1 PROCESSOR SIGNALS

D0 - D15 (input/output/high impedance) DATA 0 - 15 (Positive Logic)

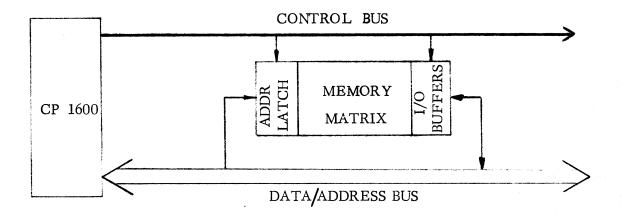

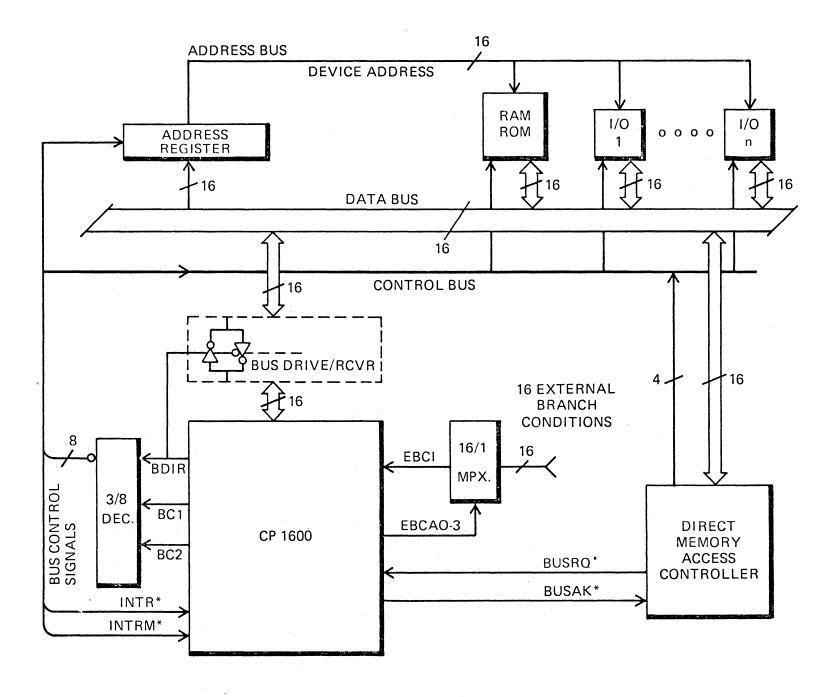

These 16 signals comprise the 16-bit bidirectional bus used by the CPU to send both data and addresses to the external subsystems and receive data and instructions from the external subsystems, i.e., memory, printers, keyboards, displays, A/D and D/A converters, magnetic tape, cassettes, and other peripherals of various types. All operations on the bus involve 16-bit transfers of either data, address or instruction words.

BDIR (output) BUS DIRECTION (Positive Logic)

This signal indicates the direction of the 16-bit bidirectional bus at the CPU. A logic "1" (High) indicates that D0-D15 are outputting to the bus. A logic "0" (Low) indicates that D0-D15 are either inputting from the bus or are in a high impedance state.

BC1, BC2 (outputs) BUS CONTROL 1, 2 (Positive Logic)

These signals in conjunction with BDIR are used to control all external bus operations. In simple systems, they can be used directly as control signals while in more elaborate ones they can be decoded in a single 3 to 8 decoder to provide all eight external bus control functions listed below:

| BC1 | BC2 | BDIR | BUS<br>CONTROL | FUNCTION                                                                                                                                                                                                                                                                                                   |

|-----|-----|------|----------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| .0  | 0   | 1    | BAR            | BUS TO ADDRESS REGISTER This signal is used<br>to load the contents of the bus into the external<br>address register. D0-D15 are in an output mode.                                                                                                                                                        |

| 0   | 1   | 1    | DWS            | DATA WRITE STROBE This signal is used as a write enable for memory or any peripheral device. D0-D15 are in an output mode.                                                                                                                                                                                 |

| 1   | 0   | 1    | DW             | DATA WRITE This signal is functionally identical<br>to DWS except that it occurs one machine cycle<br>time prior to DWS. It is used for extended write<br>operation purposes. D0-D15 are in an output mode.                                                                                                |

| 1   | 1   | 1    | INTAK          | INTERRUPT ACKNOWLEDGE This signal denotes<br>CPU acceptance of an interrupt and is used by the<br>interrupting devices to resolve priority. The<br>INTERRUPT SEQUENCE of the internal CPU state<br>timing logic commences with this acknowledgement.<br>Further details of the interrupt service are given |

| BC1 | BC2 | BDIR | BUS<br>CONTROL | FUNCTION                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

|-----|-----|------|----------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|     |     |      |                | in the section on INTERNAL CPU ARGHITECTURE.<br>D0-D15 are in an output mode.                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| 0   | 1   | 0    | IAB            | INTERRUPT ADDRESS TO BUS This signal which<br>occurs during the INTERRUPT SEQUENCE of the<br>CPU, serves to gate the starting address of the<br>interrupt service routine for the acknowledged<br>interrupting device onto the bus. D0-D15 are in<br>an input mode. The CPU will input this starting<br>address into the PC to commence execution of the<br>service routine. IAB also occurs during the power-<br>up initialization sequence to input the starting ad-<br>dress of the main program to the PC. |

| 1   | 0   | 0    | ADAR           | ADDRESSED DATA TO ADDRESS REGISTER<br>This signal causes the addressed contents of<br>memory to be gated onto the bus and strobed into<br>the address register. It is activated during all in-<br>structions which specify direct addressing. D0-<br>D15 are in the high impedance state.                                                                                                                                                                                                                      |

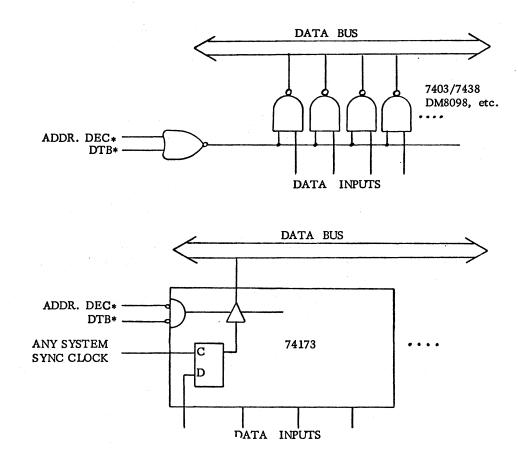

| 1   | 1   | 0    | DTB            | DATA TO BUS This signal is used to gate data<br>from memory or any peripheral device onto the<br>bus. Data in this sense can mean instructions,<br>addresses, or data. D0-D15 are in an input mode.                                                                                                                                                                                                                                                                                                            |

| 0   | 0   | 0    | NACT           | NO ACTION This signal indicates the CPU is not using the bus. D0-D15 are in the high impedance state.                                                                                                                                                                                                                                                                                                                                                                                                          |

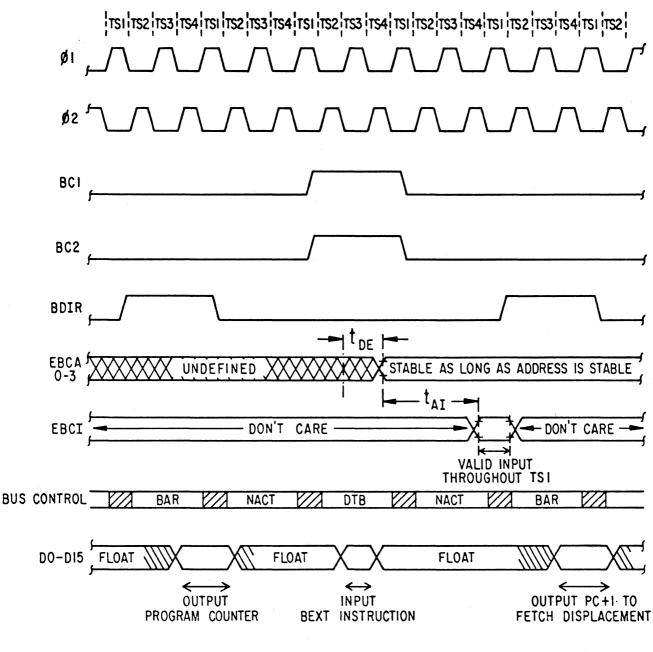

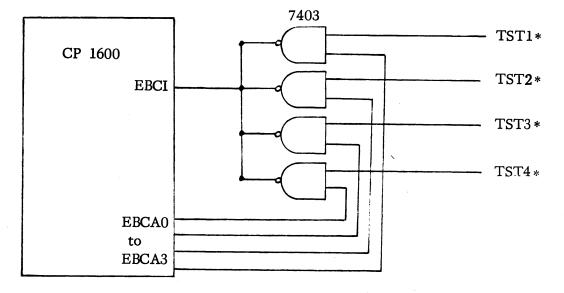

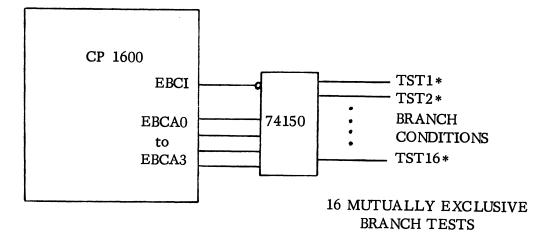

EBCA0, EBCA1, EBCA2, EBCA3 (outputs) EXTERNAL BRANCH CONDITION ADDRESS 0, 1, 2, 3 (Positive Logic)

These lines are the buffered outputs from the 4 least significant bits of the instruction register (bits 0-3) and are used to externally select one of sixteen digital states to be sampled by the CPU during the execution of the BEXT (Branch on EXTernal) instruction.

EBCI (input) EXTERNAL BRANCH CONDITION IN (Positive Logic)

This is the return signal of the 1 of 16 selection made by EBCA 0, 1, 2, 3. It is high active such that a logic "1" (High) would test as true and cause the branch to occur as part of the BEXT instruction. A logic "0" would not allow a branch to occur.

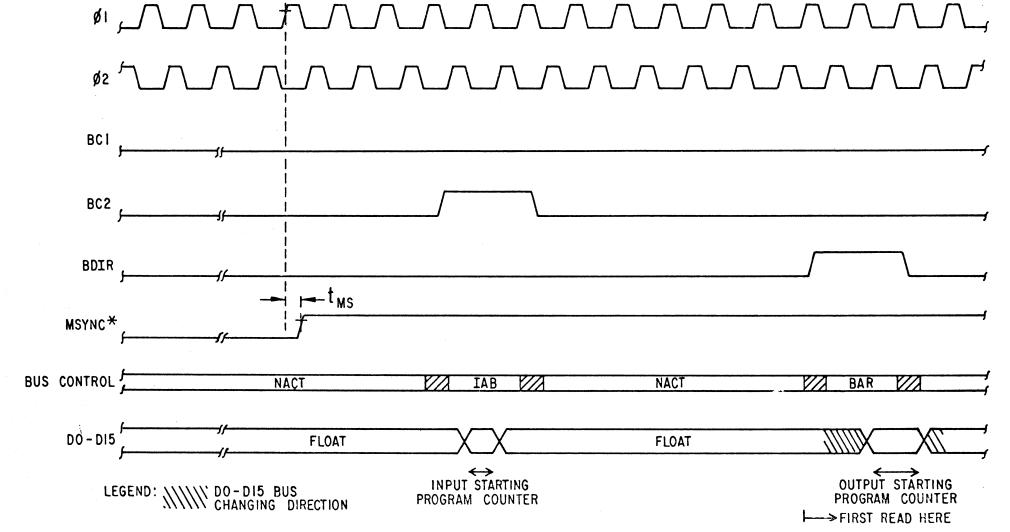

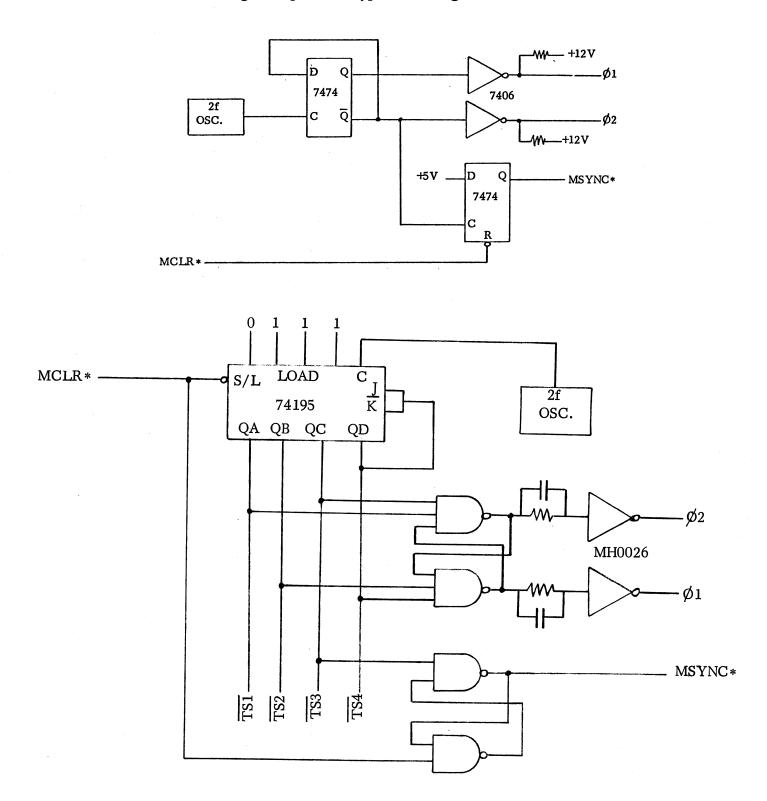

# MSYNC\* (input) MASTER SYNC (Negative Logic)

This signal is used to synchronize the internal clock generator logic to the main  $\emptyset 1$ ,  $\emptyset 2$  clock phases. Synchronization is achieved by remaining active (low) for at least ten milliseconds after power is applied to the CPU and becoming inactive (high) on any rising edge of a  $\emptyset 1$  clock. That  $\emptyset 1$  clock corresponds to an internal TS3. This signal also disables the interrupt system.

#### VDD

Nominal 12 volts power supply input to the CPU.

#### VCC

Nominal 5 volts power supply input to the CPU.

VBB Nominal -3 volts power supply input to the CPU.

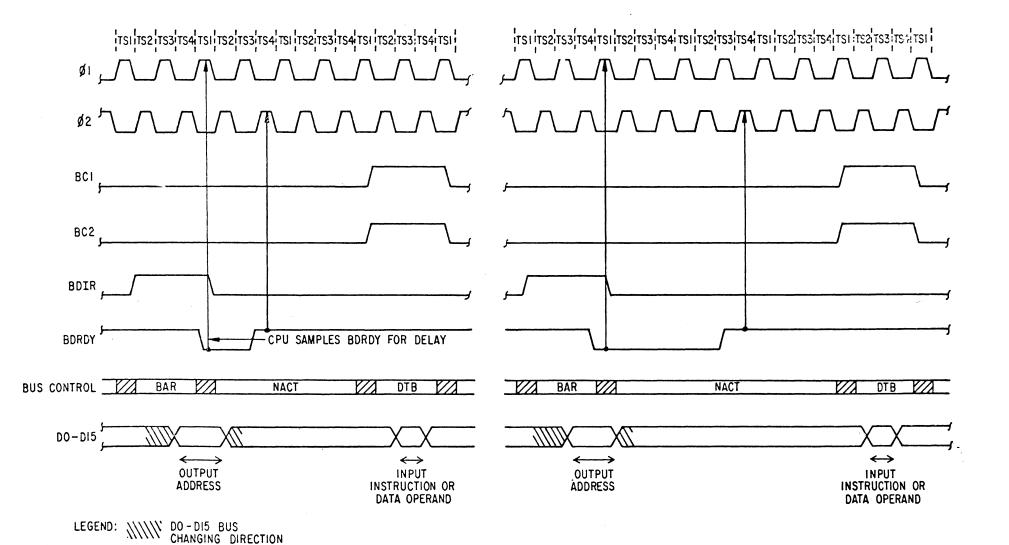

BDRDY (input) BUS DATA READY (Positive Logic)

This signal is used to make the CPU 'wait' and resynchronize itself to peripheral subsystems that cannot respond to requests for reads and writes at full CPU speed. This is intended primarily for synchronization to slow speed memories. The duration of the 'wait' period must be less than 40 microseconds to preserve the dynamic state of the CPU.

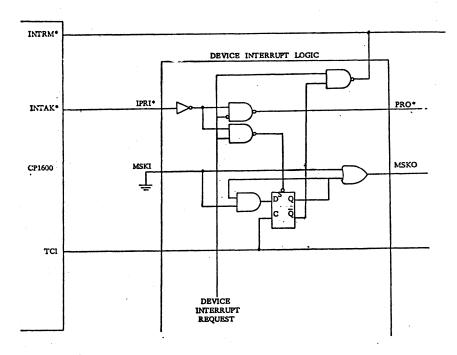

INTR\*, INTRM\* (inputs) INTERRUPT REQUEST\* (Negative Logic) INTERRUPT REQUEST MASKABLE\* (Negative Logic)

These two signals are low active signals that request the CPU to honor an interrupt at the completion of any interruptable instruction under the follow-ing conditions.

- a) INTR\* is always honored by the CPU and hence is the highest priority interrupt request line.

- b) INTRM\* is honored by the CPU only if the internal CPU interrupt flipflop, INTFF, is set. This flip-flop is controlled via the EIS and DIS instructions and several others that have similar capability as described in the instruction set.

The CPU will enter the INTERRUPT SEQUENCE if either INTR\* is active or if INTRM\* is active and INTFF is set. During this sequence, the CPU will store the PC onto the top of the memory stack and resolve interrupt device priority by enabling INTAK. This is followed by inputting the starting address of the interrupt service routine from the appropriate interrupting device into the PC by enabling IAB. The next instruction is fetched from the location pointed to by the new PC and execution of the service routine begins from that point.

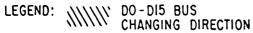

TCI (output) TERMINATE CURRENT INTERRUPT (Positive Logic)

This high active pulse signal is generated via the TCI instruction to terminate the highest priority interrupt presently in service.

$\emptyset$ 1,  $\emptyset$ 2 (inputs)

These signals supply the high-level, high-speed, non-overlapping two phase clocks to the CPU.

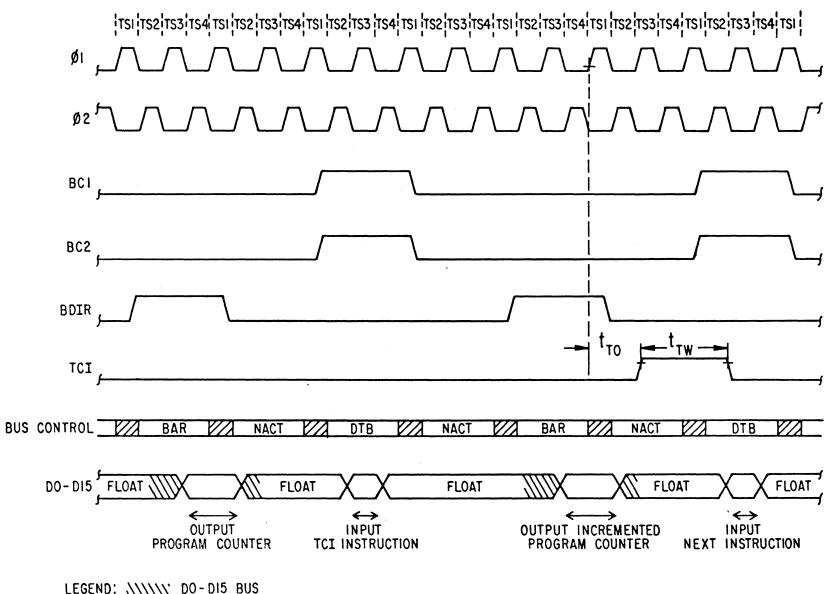

PCIT\* (input/output) PROGRAM COUNTER INHIBIT\*/TRAP\* (Negative Logic)

This pin provides two functions.

- a) As an input, this signal is a low active signal that prevents the incrementation of the program counter (R7) during the fetch phase of all instructions. Care should be used when utilizing this function during multiword instructions.

- b) As an output, this signal will generate a low active pulse during the execution of the SIN (Software INterrupt) instruction. Properly used, this signal can be returned to the CPU by the interfacing hardware as an interrupt request on either of the INTR\* or INTRM\* input pins. The interrupt will be acknowledged at the end of the SIN instruction.

These functions will not interact with each other under normal operation. The Pin Timing Diagrams in Section 2.3 will precisely describe the timing of each function.

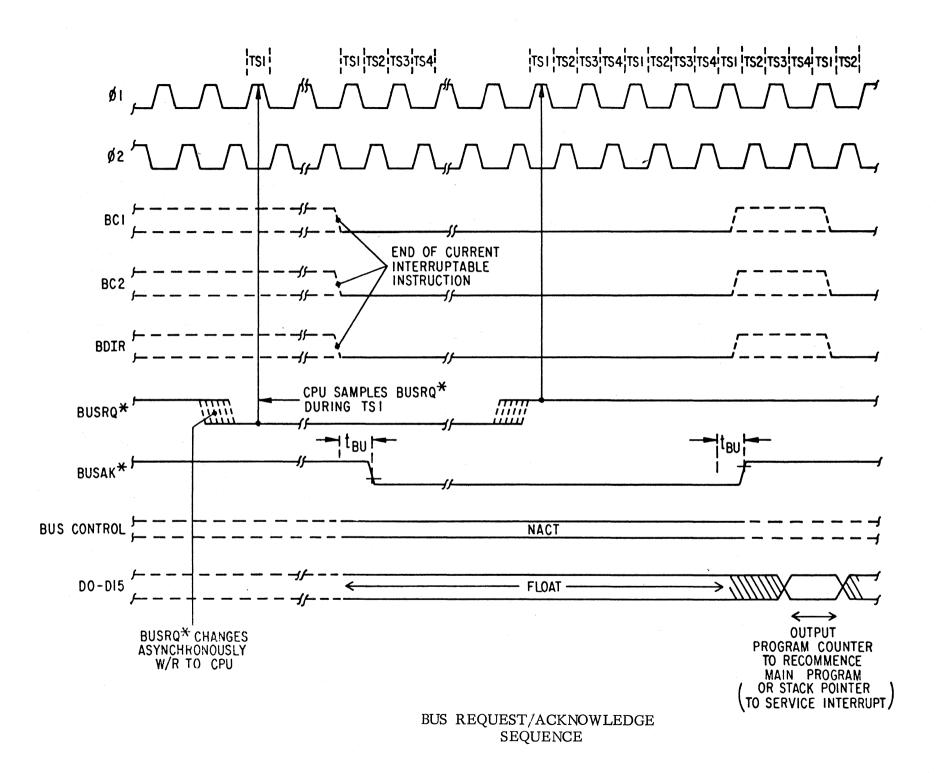

BUSRQ\* (input) BUS REQUEST\* (Negative Logic)

This signal is low active and causes the CPU to relinquish all control of the bus to allow other devices to carry out direct bus transfer operations. The CPU grants use of the bus only after the completion of an interruptable instruction (refer to the instruction listings for those instructions which are interruptable and those which are not). The CPU signifies release of the bus by causing BUSAK\* to go low and the CPU will remain in this condition until the external device releases BUSRQ\*.

BUSAK\* (output) BUS ACKNOWLEDGE\* (Negative Logic)

This is a low active signal used to inform external devices that the bus has been released by the CPU in response to the BUSRQ\* signal.

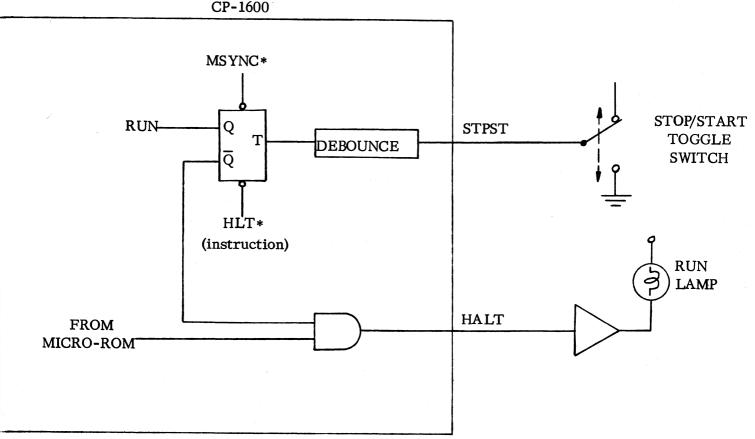

# STPST ↓ (input) STOP START (Negative Edge Triggered)

This is an edge-triggered signal used to control the running condition of the CPU. If the CPU is presently running, the negative transition of STPST  $\downarrow$  will cause the CPU to stop but only after the completion of an interruptable instruction. The CPU will generate a high active HALT signal acknowledg-ing the stopped mode. The next negative transition of STPST  $\downarrow$  will cause the CPU to return to the run mode. The HALT output will then return to a logic "0" (Low) condition.

HALT (output) HALT (Positive Logic)

This is a high active signal indicating that the CPU is in the stopped mode. This mode can occur by either the toggle action from the STPST input or by the execution of a HALT instruction by the CPU.

#### 2.2 INTERNAL CPU ARCHITECTURE

The CP 1600 is a general register oriented, central processing unit consisting of eight 16-bit registers. These registers may be used as accumulators or as addressing pointers to locations external to the CPU. R7 and R6 have special characteristics which distinguish them from the other registers. R7 serves as the program counter (PC) and points to the next instruction to be executed. R6 serves as a stack pointer (SP) which points to the next available location in the "last-in, first-out" stack maintained anywhere in main memory.

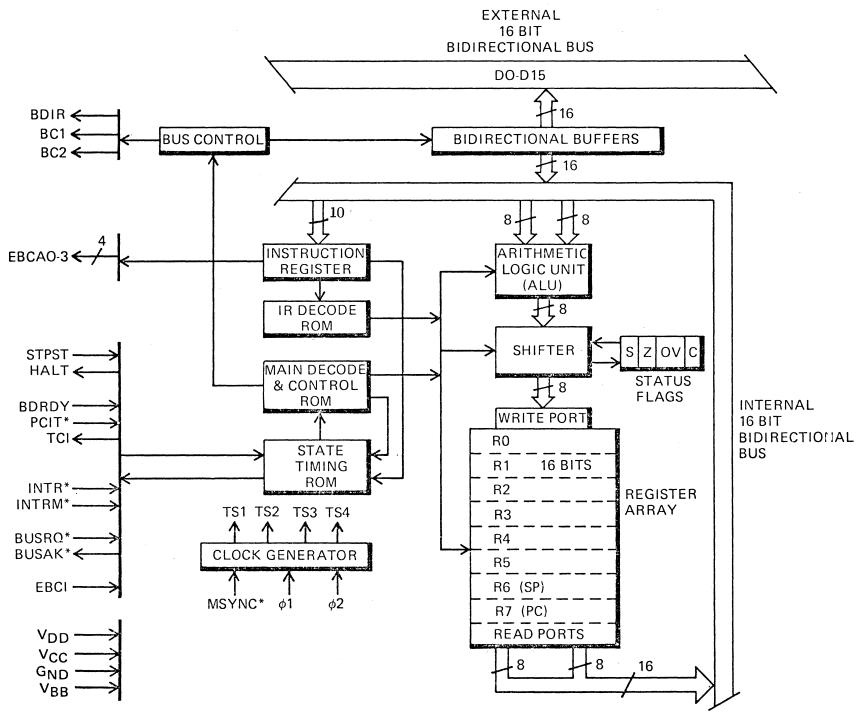

#### A. Basic Functional Blocks

A basic internal block diagram of the CP 1600 showing major subsystems and data flow is shown in Figure 2-2. It is noted that all data transfers within the machine are performed on 16-bit words processed in two 8-bit bytes. Internally, the architectural effect of this byte serial technique is to organize all data paths as 8 bits in width. In communicating with external devices, however, the CPU transfers 16 bits in parallel.

The major logic blocks through which all data flow are the Arithmetic Logic Unit (ALU), Shifter, Register Array, and the Internal 16-bit Bus.

The ALU is the primary data processing element of the CPU. It accepts two data words each 8 bits wide from the internal 16-bit bus and produces an 8-bit resultant.

The ALU passes the resultant to the Shifter which is also 8 bits wide. The Shifter can transfer data to the register array transparently or can skew data one bit position right or left. The Shifter in combination with the ALU can effect changes in the four status bits which monitor CARRY OUT from the most significant bit of the resultant, ARITHMETIC OVERFLOW, SIGN DETECT, and ZERO DETECT.

The Register Array is comprised of the eight 16-bit registers with one 8-bit write port and two 8-bit read ports. The write port can direct data to any one of the eight registers and then either to that register's lower or upper 8-bit byte. The read ports can simultaneously output to the internal bus any two byte combination, be they from the same register, different registers, left or right byte.

The Internal 16-bit Bidirectional Bus is the primary link for all information transfers between the CPU and the external world. Communications between the internal bus and the external bus are governed by the bus control signals BC1, BC2, and BDIR.

FIG. 2-2 INTERNAL BLOCK DIAGRAM

#### B. Processor Timing

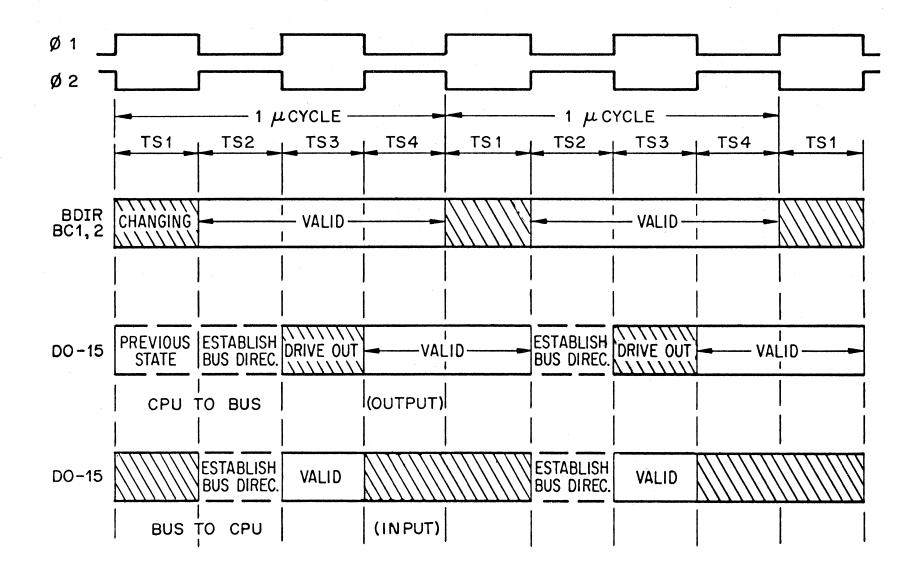

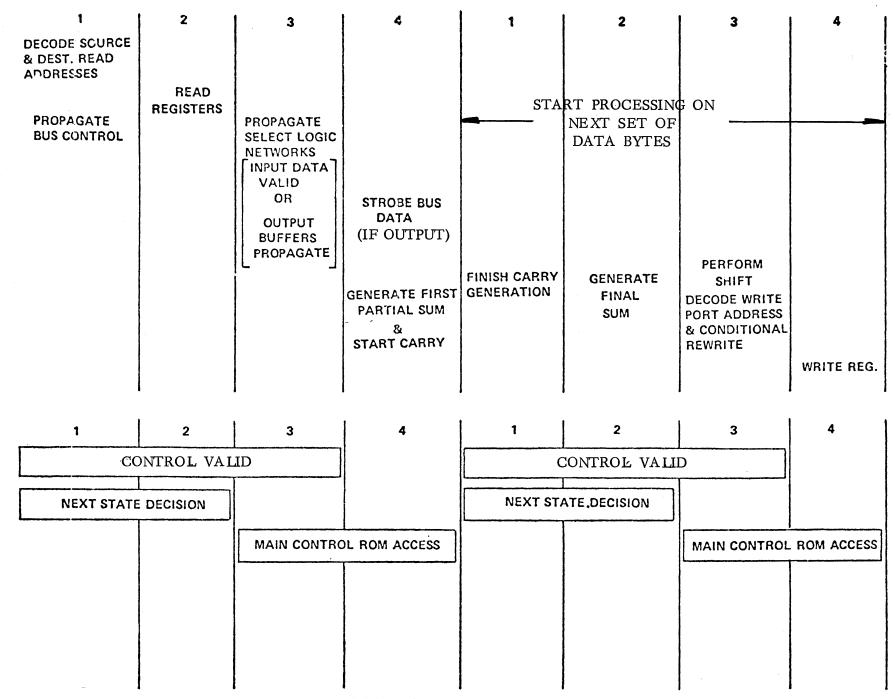

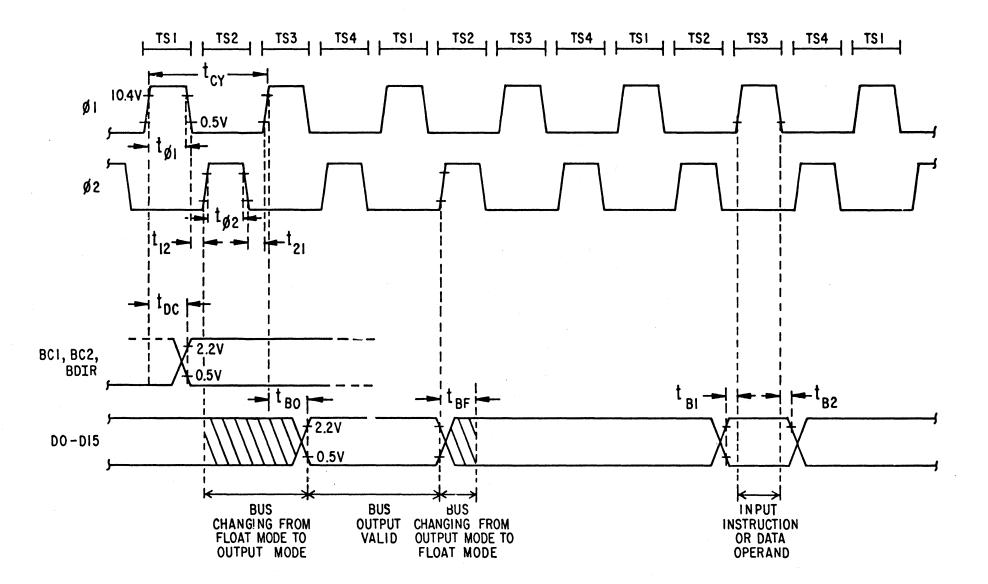

The sequential operation of the CPU is governed by an internal State Timing ROM. This network generates next addresses to the Main Decode and Control ROM. It maps these addresses from the Instruction Register contents and makes next address decisions based on conditions in the machine and/or the present microinstruction. The Main Decode and Control ROM generates 21-bit microinstructions or micro states during each processor cycle. These micro states are grouped into various Fetch states, Address states, Execute states, Wait states, states which control the Interrupt and Bus Request Sequences, and others. Each micro state time is defined as four internal time slots - TS1, TS2, TS3, TS4 - as generated by the Clock Generator from the external non-overlapping clocks. See Figure 2-3.

If the CPU is driven by a 5 MHz, two-phase clock system as shown, then the duration of each micro state is 400 nanoseconds.

The State Timing ROM operates in parallel with the data processing logic thus keeping the Control ROM synchronous with the data flow operations. Thus, during any internal state time, the Control ROM and the Instruction Register Decode ROM are dictating the data processing functions in the ALU, Shifter, and the Register Array.

The CP 1600 achieves high internal processing speed through the use of microinstruction overlapping and data pipelining (Fig. 2-4). During each 400 nanosecond cycle, a 21-bit control word is executed while the next address decision is made and the new control word accessed. In addition, the Register/ALU data loop is pipelined so that two sets of byte pairs are being processed during each cycle. Before the result of an ALU operation is complete and returned to the Registers, the next operation on new data has already started.

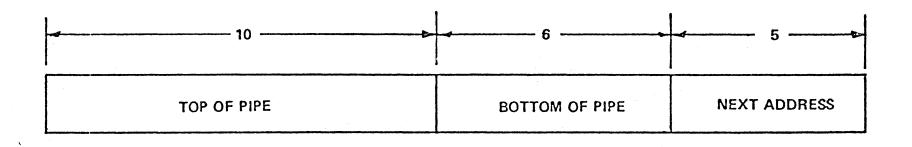

In order to achieve this "data streaming" effect, the microinstruction word of the processor is divided into three major fields (Fig. 2-5). The first controls the top of the pipe which includes the READ PORTS and front end of the ALU logic. The second controls the bottom of the pipe which includes the lookahead carry network, the final part of the ALU logic and shifter, and the rewrite to the registers. The third field controls the selection of the next control state.

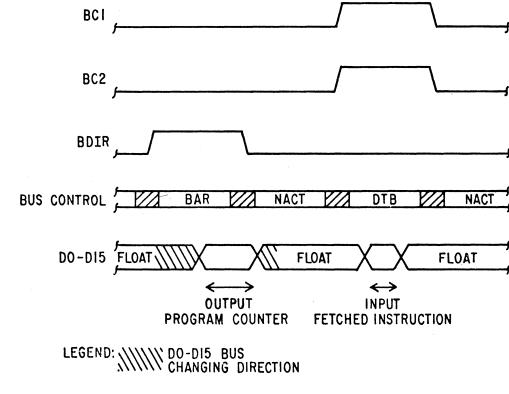

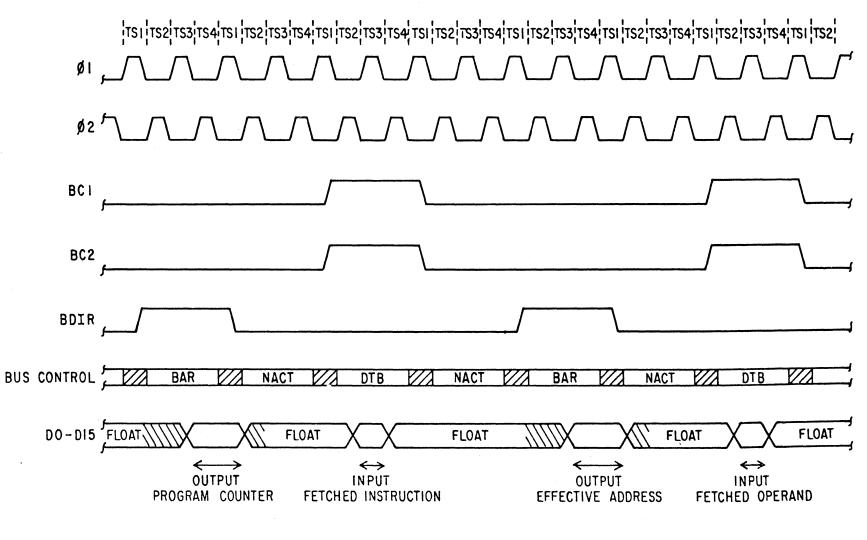

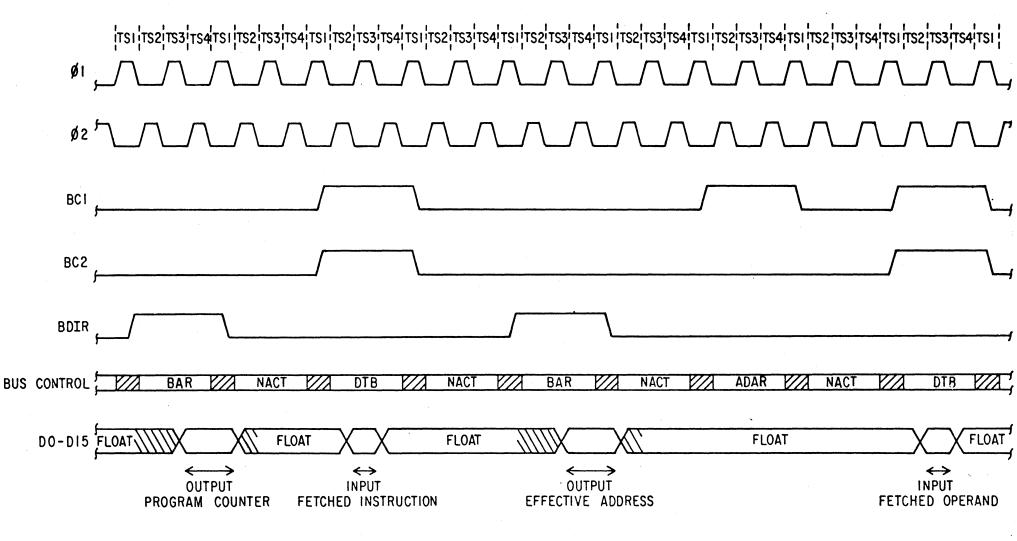

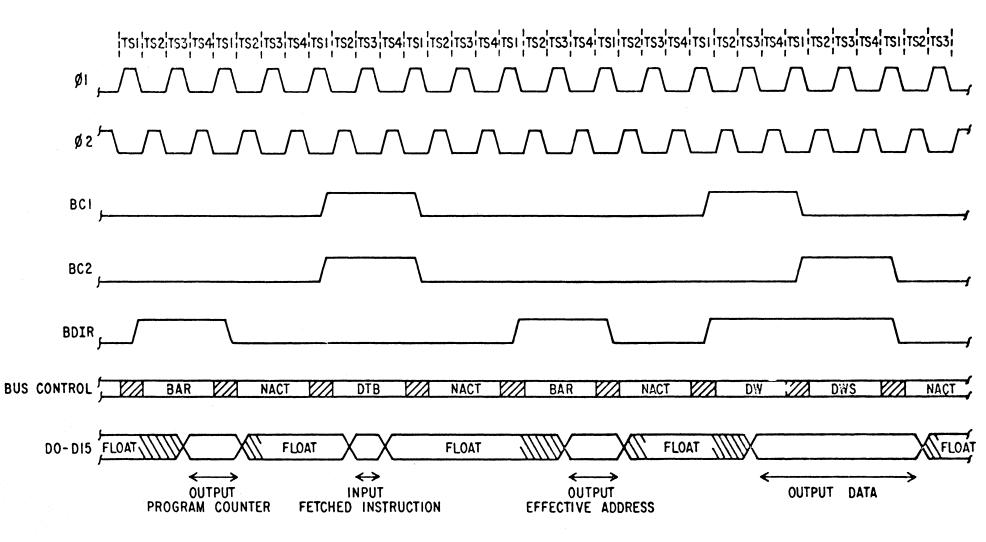

Finally, each state has its own unique pattern of bus control signals (BC1, BC2, BDIR). For example, in the first fetch state, the bus controls signals will be decoding BAR. In the next, they decode NACT, and, in the next, they decode DTB.

#### C. State Timing

Although it is not necessary for the user to understand the exact sequencing through the internal microcoded states, it is important to understand

FIG. 2-4 PIPELINE TIMING

FIG. 2-5 MICROINSTRUCTION FORMAT

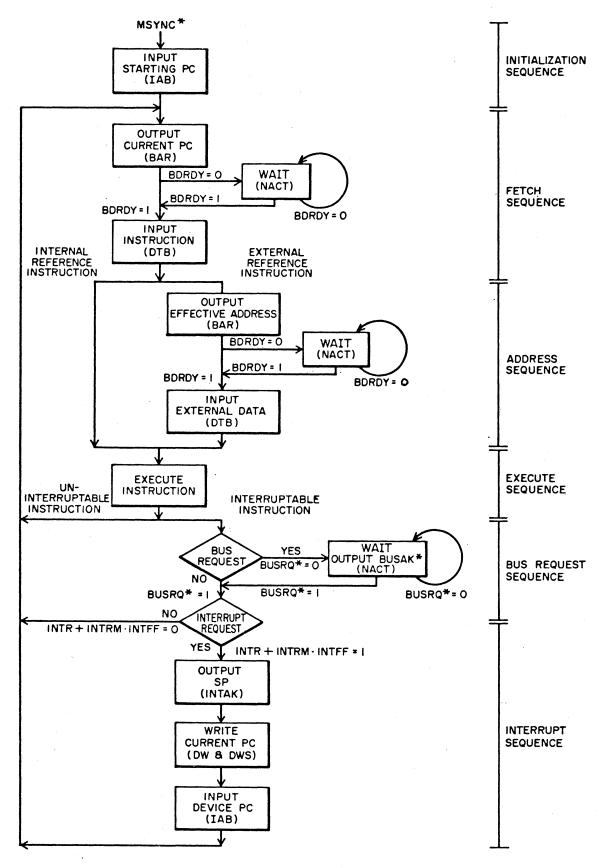

the general state flow and how it relates to the execution of instructions and their interaction with the various interfacing signals like BDRDY, BUSRQ\*, INTR\* and others. A basic state flow diagram is shown in Fig. 2-6.

There are six major state sequences through which the CPU passes: Initialization, Fetch, Address, Execute, Bus Request, and Interrupt Request sequences. Each of the sequences consist of one or more micro states (indicated by rectangular blocks). However, the decoded bus control signal in parenthesis indicates only the primary bus function to be performed during that functional operation. (Recall there is a unique set of bus control signals for each microcode state). Illustrations of the exact timing during each of these sequences is given in the "Pin Timing Diagrams" section.

#### C.1 Initialization Sequence

When power is first applied to the CPU, the MSYNC\* signal must be at an active (low) level. This will force the CPU to an inactive state in which D0-D15 are in a high impedance state with the bus control signals issuing NACT. All other signals are in their inactive state and the interrupt system is disabled. All eight internal registers and the status bits contain arbitrary, undefined data. When MSYNC\* goes inactive (high), the bus control signals issue IAB, and the CPU inputs from the bus into the PC the starting address of the main program. Note that the initialization address can be defined by the user at any desired bus address or can be the default address resulting from the logical state of the non-driven bus.

#### C.2 Fetch Sequence

The Instruction Fetch sequence will be entered after the initialization of the CPU, or after the execution of the previous instruction and the resolution of pertinent bus and interrupt requests. During the first microstate, the bus control signals issue BAR. During this state, the CPU will output the current contents of the PC onto the bus. BAR will strobe this data from the bus into the address register to fetch the instruction pointed to by the PC. Internally, the CPU increments PC and returns it to R7.

Beginning in the next micro state, the CPU will sample the BDRDY input line. If BDRDY is at a logic "1" level, the CPU will proceed to the next state where the fetched instruction will be inputted into the CPU via the signal DTB. If BDRDY is at a logic "0" level, the CPU will enter a WAIT state and remain in this state until BDRDY is brought to a logic "1" level. This WAIT state cannot be of indefinite duration; it must last no longer then 40 microseconds in order to preserve the dynamic characteristics of the CPU during this fetch sequence. The bus control signals will change to NACT throughout the WAIT state. External systems will need to utilize this WAIT state when their access times cannot meet the CPU speed requirements. As long as the CPU is in the WAIT state, it will sample the BDRDY line every microcycle (every 400 nanoseconds if the clock input is 5 MHz).

Once BDRDY is high, the CPU will issue the DTB bus signal. The external system presently addressed will gate data (in this instance the fetched instruction word) onto the bus. The instruction will be inputted to the CPU and loaded into its instruction register.

BASIC STATE FLOW DIAGRAM

FIG. 2-6 INTERNAL FLOW DIAGRAM

#### C.3 Address Sequence

The Address Sequence will only be entered if the instruction just fetched is of an External Reference type. The distinctions between external and internal reference types will be made clearer in the chapter "Instruction Set". Basically, External Reference instructions need to retrieve external data to complete execution of the instruction. For example, those instructions which specify the contents of a register to be the address of an operand are all of external reference type. Internal Reference instructions process operands already held within the registers of the CPU.

The Address Sequence is very similar to the Fetch Sequence. The CPU will begin by issuing BAR and outputting some computed effective address on the bus. The particular instruction will determine how the effective address is computed. The effective address will be gated into the address register. The CPU will then sample BDRDY exactly as before. Again, if a WAIT state is entered, its duration must be less than 40 microseconds. Once BDRDY has been resolved, the CPU will issue a DTB which will gate the retrieved data onto the bus. The CPU inputs this data which will be used as an operand in executing the instruction.

Note: This sequence becomes slightly more complex if the instruction specifies direct addressing. The CPU will issue BAR, sample BDRDY, then issue ADAR to readdress memory, sample BDRDY again, and finally issue DTB.

## C.4 Execute Sequence

After the data operands have been obtained, the CPU will execute the instruction. Execution can take as few as two microcode states or as many as six for the most complex instructions. Different types of bus control signals are activated according to instruction type. Examples are shown in the following table.

| Instruction Class   | # of Micro States | Bus Control Signals |

|---------------------|-------------------|---------------------|

| External Reference  |                   |                     |

| Input Group         | 2                 | DTB, NACT           |

| Move Out            | 3                 | DW, DWS, then NACT  |

| Double Byte Data    | 3                 | BAR, NACT, and then |

|                     |                   | DTB                 |

| Internal Reference  |                   |                     |

| Register - Register | 2                 | NACT                |

| Shift               | 2 or 4            | 2 or 4 NACT         |

#### C.5 Bus Request Sequence

If there are no Bus Requests or Interrupt Requests following the execution of the present instruction, the CPU will return to the Fetch Sequence and fetch the next instruction from memory.

If some external device has activated the BUSRQ\* input line (by pulling it low) prior to the completion of the execution of the current interruptable instruction, the CPU will honor the Bus Request by causing the output signal BUSAK\* to go low. The CPU will enter a WAIT state and remain in this state until BUSRQ\* is brought to a logic "1" level. This WAIT state <u>can</u> be of indefinite duration. BUSAK\* will be low for **a**s long as the <u>CPU</u> is in this state and the CPU will not use the bus; the bus control signals will be issuing NACT. All other signals will be in their inactive state.

The BUSRQ\* input signal can be activated asynchronously with respect to the CPU clocks. The CP 1600 digitally synchronizes BUSRQ\* during every TS1 time.

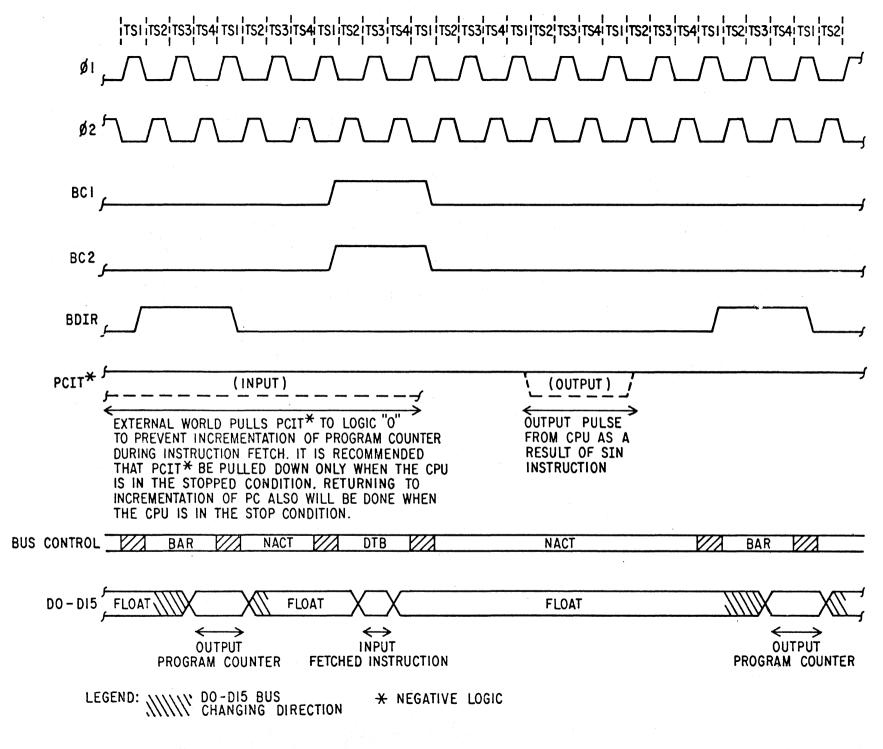

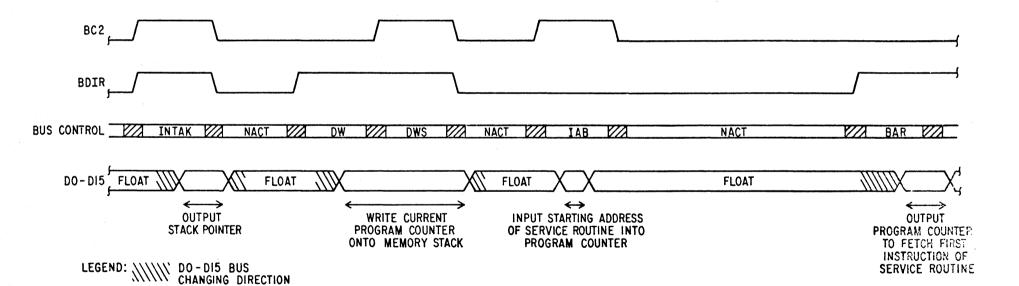

# C.6 Interrupt Sequence

The CPU will enter its Interrupt Sequence after all bus requests have been resolved and either of the following conditions have been met:

- a) The INTR\* input signal has been activiated, i.e., it has been pulled to a logic "0" level in sufficient time for the CPU to recognize the input as a valid interrupt request; or,

- b) The INTRM\* input signal has been similarly activated AND the internal interrupt flip-flop, INTFF, is set (enabled).

Once an interrupt request has been accepted by the CPU, the CPU performs the following functions automatically:

- 1. The first micro state will issue the bus control signal INTAK. The presence of this signal denotes acceptance by the CPU of the interrupt request and can be used by the peripheral devices to resolve interrupt priority. During this state, the CPU will output the current contents of Register 6, the Stack Pointer, to the Address Register in preparation for saving the program counter on the Stack.

- 2. The CPU will then output the PC as data to be stored and issue bus signals DW and DWS to write the Program Counter into the location pointed to by the Stack Pointer. That is, the CPU will store the PC into the top of the STACK. The Stack Pointer will be incremented after this store operation.

3. Finally, the CPU will issue bus signal IAB which will bring the starting address of the interrupt service routine into the program counter. The CPU will then return to the Fetch Sequence and execution continues in normal fashion from the new PC supplied by the interrupting device.

Again, in a manner similar to that of the BUSRQ\* line, the CPU samples the INTR\* and INTRM\* inputs every TS1 time. In addition, the CPU will honor Bus Requests before it will honor Interrupt Requests.

## 2.3 TIMING DIAGRAMS

The functional operation and relative timing of all CP 1600 sequences are shown in the following diagrams. These include:

Initialization Sequence Instruction Fetch Instruction Fetch & Data Access Write Sequence External Condition Test Sequence TCI Instruction Timing PCIT \* Pin Timing Interrupt Sequence BUSRQ/BUSAK Sequence BDRDY Operation

# INITIALIZATION SEQUENCE

START HERE |TSI |TS2 |TS3 |TS4 |TSI |TS2 |TS3 | |TSI |TS2 |TS3 |TS4 |TSI

ø2'

INSTRUCTION FETCH & DATA ACCESS (INDIRECT REG. MODE)

LEGEND: UNIT DO - DIS BUS CHANGING DIRECTION

INSTRUCTION FETCH & DATA ACCESS (DIRECT ADDR. MODE)

MVO TIMING (WRITE OPERATION)

BRANCH ON EXTERNAL INSTRUCTION

TCI INSTRUCTION TIMING

PCIT\* TIMING

INTERRUPT SEQUENCE

BCI

.

.

BUS DATA READY (BDRDY) TIMING

# 2.4 ELECTRICAL SPECIFICATIONS (Tentative)

### Maximum Ratings

VDD, VCC, GND, and all other input or output voltages with respect to VBB

Storage Temperature

Temperature Under Bias

Exceeding these ratings could cause permanent damage to the device.

-0.3V to +18.0V $-55^{\circ}C$  to  $+150^{\circ}C$

$0^{\circ}C$  to  $70^{\circ}C$

Functional operation at these conditions is not implied - operating conditions are specified below.

# Recommended DC Operating Conditions & Characteristics

All signals referenced to GND, unless otherwise noted.  $T_A = 0^{\circ}C$  to  $70^{\circ}C$ , unless otherwise noted.

|                                                             | Symbol                  | Min.                 | Typ.                | Max.                 | Uni         | ts Conditions                                                                            |

|-------------------------------------------------------------|-------------------------|----------------------|---------------------|----------------------|-------------|------------------------------------------------------------------------------------------|

| Supply Voltage                                              | V D D<br>V C C<br>V B B | 11.4<br>4.75<br>-2.7 | 12.0<br>5.0<br>-3.0 | 12.6<br>5.25<br>-3.3 | V<br>V<br>V | I <sub>DD</sub> =70mA (typ)<br>I <sub>CC</sub> =12mA (typ)<br>I <sub>BB</sub> =1mA (typ) |

| Clock Input High Voltage                                    | VIHC                    | 10.4                 |                     | VDD                  | V           |                                                                                          |

| Clock Input Low Voltage                                     | VILC                    | 0                    |                     | .5                   | v           |                                                                                          |

| Input Logic High Voltage<br>D0-D15<br>BDRDY<br>All other    | VIH                     | 2.4<br>3.0<br>2.4    |                     | VCC<br>VCC<br>VCC    | V<br>V<br>V |                                                                                          |

| Input Logic Low Voltage                                     | VIL                     | 0                    |                     | .65                  | V           |                                                                                          |

| Output High Voltage                                         | VOH                     | 2.4                  |                     |                      | V           | IOH=100µA                                                                                |

| Output Low Voltage<br>D0-D15<br>BDIR, BC1, BC2<br>All other | VOL                     |                      |                     | .5<br>.45<br>.45     | V<br>V<br>V | IOL=1.6mA<br>IOL=2.0mA<br>IOL=1.6mA                                                      |

# A. C. Characteristics

$T_A = 0^{\circ}C$  to  $70^{\circ}C$ ,  $V_{DD} = 12V \pm 5\%$ ,  $V_{CC} = 5V \pm 5\%$ ,  $V_{BB} = -3 \pm 10\%$ , unless otherwise noted.

All notations refer to the BUS TIMING DIAGRAM unless otherwise noted.

|                                                          | Symbol          | Min. | <u>Typ</u> .*                                                                                                   | Max.        | <u>Units</u> | Conditions            |

|----------------------------------------------------------|-----------------|------|-----------------------------------------------------------------------------------------------------------------|-------------|--------------|-----------------------|

| Pulse Width of Ø1                                        | <sup>t</sup> Ø1 | 70   |                                                                                                                 |             | n <b>s</b>   |                       |

| Pulse Width of Ø2                                        | <sup>t</sup> Ø2 | 70   |                                                                                                                 |             | ns           |                       |

| Clock Delay between<br>Ø1 & Ø2                           | t <sub>12</sub> | 0    |                                                                                                                 |             | ns           |                       |

| Clock Delay between<br>Ø2 & Ø1                           | t <sub>21</sub> | 0    |                                                                                                                 |             | ns           |                       |

| Clock Period                                             | t <sub>cy</sub> | .2   |                                                                                                                 | <b>5.</b> 0 | μs           |                       |

| Clock Rise & Fall Times                                  | tr, tf          |      |                                                                                                                 | 15          | ns           |                       |

| D0-D15 Bus Delay from<br>Ø1 (float to output)            | t <sub>BO</sub> |      | 1997 - 1997 - 1997 - 1997 - 1997 - 1997 - 1997 - 1997 - 1997 - 1997 - 1997 - 1997 - 1997 - 1997 - 1997 - 1997 - | 70          | ns           |                       |

| D0-D15 Bus Input<br>from Ø2 (output to<br>float)         | <sup>t</sup> BF |      |                                                                                                                 | 50          | ns           | 1 TTL & 25 pf<br>load |

| BC1, BC2, BDIR Output<br>Delay from Ø1                   | <sup>t</sup> DC |      |                                                                                                                 | 70          | ns           |                       |

| D0-D15 Bus Input<br>Set-up Time before<br>Ø1             | t <sub>B1</sub> | 0,   |                                                                                                                 |             | ns           |                       |

| D0-D15 Bus Input<br>Hold Time after Ø1                   | t <sub>B2</sub> | 10   |                                                                                                                 |             | ns           |                       |

| MSYNC* Input Delay<br>from Ø1                            | t <sub>MS</sub> |      |                                                                                                                 | 30          | ns           |                       |

| BUSAK * Output Delay<br>from Ø1                          | t <sub>BU</sub> |      | 150                                                                                                             |             | ns           |                       |

| TCI Output Delay<br>from Ø1                              | <sup>t</sup> TO |      | 200                                                                                                             |             | ns           | 1 TTL & 25 pf<br>load |

| TCI Pulse Width                                          | <sup>t</sup> TW |      | 300                                                                                                             |             | ns           |                       |

| EBCA Output Delay from<br>input of BEXT instruc-<br>tion | t <sub>DE</sub> |      |                                                                                                                 | 150         | ns           |                       |

| EBCA to EBCI Input Delay 25°C and nominal supply         |                 |      |                                                                                                                 | 400         | ns           |                       |

# CAPACITANCE

$T_A = 25^{\circ}C; V_{DD} = 12.0V, V_{CC} = 5.0V, V_{BB} = -3.0V$

$t \phi_1 = t \phi_2 = 100 \text{ ns}$

|                                          | Symbol           | Min. | Typ.   | Max.     | <u>Units</u> |

|------------------------------------------|------------------|------|--------|----------|--------------|

| Ø1 Clock Capacitance                     | C <sub>Ø1</sub>  |      | 20     | 30       | pf           |

| Ø2 Clock Capacitance                     | C <sub>Ø2</sub>  |      | 20     | 30       | pf           |

| Input Capacitance<br>D0-D15<br>All other | C <sub>in</sub>  |      | 6<br>5 | 12<br>10 | pf<br>pf     |

| Output Capacitance                       | C <sub>out</sub> |      |        |          |              |

| D0-D15 bus high<br>impedance state       |                  |      | 8      | 15       | pf           |

#### Notes on Some Timing Signals

1. BDRDY

The CPU samples the BDRDY input line every TS1 immediately following every micro state in which a BAR or ADAR bus control signal is issued. The following details apply:

- a) BDRDY must go to logic low requesting a wait state no later than 50 nsec into TS1. It will never go to logic low in any time slot other than TS1.

- b) BDRDY must stay low for a minimum of 50 nsec.

- c) BDRDY may go to a logic "1" level asynchronously to the CPU clocks. The CPU will synchronize this signal during TS4.

- 2. STPST↓

The STPST  $\oint$  signal is sensitive to high-to-low transitions. The width of the pulse at the low level is 200 nsec minimum, with a maximum frequency of 800 kHz.

#### CHAPTER 3

#### CP-1600 INSTRUCTION SET

#### 3.0 GENERAL INSTRUCTION FORMAT

The basic instruction word format for the CP 1600 microprocessor consists of 10 bits located in the low order bit positions of a 16-bit processor word. The high order 6 bits of every 16-bit word supplied to the CP 1600 as an <u>in-</u> <u>struction word</u> are ignored by the internal microcontrol logic. This results in a compact, highly efficient 10-bit instruction word that can be implemented directly in a single 10-bit wide ROM instead of dual 8-bit wide ROMs for those systems requiring the ultimate in ROM bit efficiency. The 8 internal working registers, all data operands, displacement constants, and arithmetic and logical operations are implemented to full 16-bit significance providing the performance, flexibility, and efficiency of 16-bit operation.

The 10-bit instruction word is divided into 3 functional fields to which most instructions conform. This is shown in Fig. 3.0.1.

| 15 10        | 98              | 7 | 6 | 5 | 4  | 3 | 2 | 1  | 0 |

|--------------|-----------------|---|---|---|----|---|---|----|---|

| Future Use * | Jse * Operation |   |   |   | F1 |   |   | F2 |   |

\*This field is not implemented by the microcontrol logic in the CP1600.

#### FIG. 3.0.1

The most significant 4 bits of the CP 1600 instruction word is the Operational Field which provides 16 basic operations. The 16 operations are evenly divided into 2 groups of 8 instructions each; the External Reference group and the Internal Reference group.

## 3.1 INSTRUCTION DESCRIPTION

All Series 1600 symbolic instructions are expressed as statements containing an operator (OP Code) and in most cases one or two operands (Source/Address Mode and Destination). In general, the first three characters of an operator mnemonic represent the operation to be performed while the last character represents the addressing mode, such as ADDR for ADD Registers. The following description of instructions depicts both the symbolic format and also the binary translation. The timing, status register change, and instruction description is also shown.

The timing of each instruction is shown in terms of CPU cycle times. In addition to the basic number of cycle times for each instruction there are also potential wait times for every memory access associated with that instruction. Each wait time is dependent on the access time of the particular segment of memory being accessed. If the CPU cycle time is 400 nanoseconds and the memory speed is 1-700 nanoseconds, then W=0; if the memory speed is 701-1100 nanoseconds, then W=1; and if the memory speed is 1101-1500 nanoseconds then W=3; etc. For example, each instruction fetch has an associated wait time as does each word of a multi word instruction. If data is addressed during execution of an instruction, this additional memory access also has an associated potential wait time. Thus for an external reference instruction that is itself accessed from fast memory but its data is accessed from slow memory the following might hold:

> Number of Cycles = 8 + 2W = 8 + W + W= 8 + 0 + 2= 10 cycles total

# 3.1.1 SYMBOLIC NOTATION

The following symbolic notation is used in all Series 1600 instruction documentation:

| Address Modes: | R<br>'blank'<br>@<br>I                                |   | register<br>direct address<br>indirect address<br>immediate data                                                                                                                                                                      |

|----------------|-------------------------------------------------------|---|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Functions:     | +<br>▼<br>↓<br>∧<br>()<br>↓                           | - | addition<br>subtraction<br>inclusive OR<br>exclusive OR<br>AND<br>contents of<br>is replaced by<br>optional operand                                                                                                                   |

| Status:        | S<br>Z<br>C<br>OV                                     | - | Sign bit<br>Zero bit<br>Carry bit<br>OVerflow bit                                                                                                                                                                                     |

| Operands:      | SSS<br>DDD<br>MMM<br>R<br>RR<br>RRR<br>N<br>S<br>EEEE |   | Source Register<br>Destination Register<br>Address Mode (register)<br>Last bit of Register address<br>Register (0-3)<br>Register (0-7)<br>Number of Shifts (1 or 2)<br>Sign of Address Displacement<br>External Condition Code (0-15) |

## 3.1.2 OPERATION OF STATUS BITS

During arithmetic and logical operations in the **C**PU, the ALU Status Bits are used to monitor and record four characteristics of the resultant data. These bits are Carry (C) out of the ALU, arithmetic OVerflow (OV) from the ALU, Zero (Z) result from the output of the Shifter, and Sign (S) detect from the output of the Shifter. These bits operate in the following manner:

- C set if the result of an ADD, SUB, or CMP instruction produces a carry; cleared otherwise (SUB and CMP are performed by addition of two's complement of the subtrahend operand).

- OV set if the result of an ADD, SUB, or CMP instruction produces arithmetic overflow (two's complement notation); cleared otherwise (SUB and CMP are performed by addition of two's complement of the subtrahend operand).

- z set if the result of an operation produces an all zero result; cleared otherwise.

- S set if the result of an operation contains a "one" in the high order bit position; cleared otherwise.

#### 3.2 EXTERNAL REFERENCE INSTRUCTIONS

The External Reference instructions, which have a one in the high order bit position of the Operation Field, route data into or out of the CP 1600 to externally located bus addresses. Since a single address bus structure is utilized in the CP 1600 architecture, both memory and peripheral devices reside in the same Address Space. Only the system address allocation, as defined by the user, differentiates memory from I/O devices; therefore, no special input/output instructions are required and any External Reference instruction can access memory or peripheral devices. The CP 1600 utilizes a full 16-bit addressing structure which provides access to 65, 536 unique bus locations.

#### 3.2.1 DATA ACCESS INSTRUCTIONS

|          | 15 -  | 10     | 9 | 87          | 6     | 54          | 3     | 2            | 1    | 0              |     |       |      |       |  |

|----------|-------|--------|---|-------------|-------|-------------|-------|--------------|------|----------------|-----|-------|------|-------|--|

|          | Futu  | re Use | 1 | Oper        | ation | Мос         | le    | Des          | t.R  | eg.            |     |       |      |       |  |

| MoVe O   | ut    | (MVO)  |   | 00          | 01    | 000         | -     | - Din        |      | : add<br>ry lo |     |       |      | ct    |  |

| MoVe Ir  | 1     | (MVI)  |   | 0           | 10    | 001         | -     | - Ind        |      | •              |     |       |      | R1    |  |

| ADD      |       | (ADD)  |   | <b>.</b> 0. | 11    | 010         | _ •   | - Ind        | lire | ct ac          | ddr | ess   | thru | 1 R2  |  |

| SUBtrac  | t .   | (SUB)  |   | 1(          | 00    | 011         |       | - Ind        | lire | ct ac          | ddr | ess   | thru | R3    |  |

| CoMPar   | e     | (CMP)  |   | 10          | 01    | 100         | · - · | - Ind<br>R4. |      | ct ac<br>4+1-  |     |       | thru |       |  |

| logical  | AND   | (AND)  |   | 1           | 10    | 101         | -     | - Ind        | lire |                | ddr | ess   | thru | L     |  |

| eXclusiv | ve OR | (XOR)  |   | 1.          | 11    | <b>11</b> 0 | _     | - Sta        | ick  | thru           | Ré  | 6; Pc |      | ncre- |  |

|          |       |        |   |             |       |             |       | me           | nt i | f Inp          | out |       |      |       |  |

|          |       |        |   |             |       | 111         | -     | - Im<br>me   |      | diate<br>ry lo |     |       |      | xt    |  |

The format for 7 of the 8 External Reference instructions is shown in Fig. 3.2.1.

FIG. 3.2.1

These instructions use the lower 3 bits of the word as the register designator. This register is the source of data for output operations and the destination for data on input operations. The Mode Field of the instruction specifies the addressing mode to be used to access the Address Space. Mode 0 indicates that the contents of the next memory location is to be used directly as an external address. Modes 1, 2 and 3 indicate that registers 1, 2 and 3 respectively contain the external address. Modes 4 and 5 indicate indirect addressing through registers 4 and 5 with the contents of the register automatically incremented after use as the address; i.e., post increment. Mode 6 indicates stack operations, i.e., indirect through register 6 with the contents of the register post incremented for output operations (push) and pre-decremented for input operations (pull). The Stack is maintained by register 6 and expands upward in external memory from low address to high address. Mode 7 indicates that the next memory location holds data to be used directly; i.e., immediate data.

In order to utilize an efficient 10-bit instruction ROM and also reference 16-bit data from the same memory area, a Double Byte Data feature is available on the CP-1600. When a Set Double Byte Date (SDBD) instruction preceeds an external reference instruction, two words of memory are accessed. The least significant data byte is obtained from the low order eight bits of the first word and the most significant data byte is obtained from the low order eight bits of the second word. These bytes are then combined by the processor to form a 16-bit data word. Double byte data may be accessed via indirect addressing modes 4, 5, and 7. If modes 1, 2 and 3 are used only one word is accessed with both bytes of data obtained from the lower eight bits of the same word. Modes 0 and 6 are not supported in the double byte data operation.

## 3.2.2 CONDITIONAL BRANCH INSTRUCTIONS

The eighth instruction in the External Reference group is the Conditional Branch type which has the format shown in Fig. 3.2.2.

| 15 10                | 9 | 8        | 7          | 6  | 5 | 4        | 3 | 2          | 1           | 0  |

|----------------------|---|----------|------------|----|---|----------|---|------------|-------------|----|

| Future Use           | 1 | OP<br>(C | Co<br>000) | de | + | 4<br>I/E | ( | Cono<br>Co | diti<br>ode | on |

| Address Displacement |   |          |            |    |   |          |   |            |             |    |

FIG. 3. 2, 2

This instruction tests any one of 32 conditions and causes a branch in the program if the test has a true result. The 32 conditions are evenly divided into 2 groups of 16 each. The Internal Condition Codes comprise various tests on the state of the status register bits of the ALU while the External Condition Codes comprise 16 tests on external digital status signals of the user's choice. (Bit 4 = 1 for external.)

In case of a false result, the program continues to the next sequential instruction. When the appropriate conditions are true, the instruction transfers program control to the specified destination. The actual destination address is determined by adding or subtracting the address displacement contained in the second word of the instruction to the program counter. If the destination direction bit of the instruction (+) is zero, then the displacement is added to PC+2. If it is one, then the displacement is one's complemented and then added to PC+2.

## 3.2.3 EXTERNAL REFERENCE ADDRESSING MODES

All of the instructions in the external reference group require that data be accessed from the external Address Space of the processor. The detailed sequence for each of the various addressing modes is shown in Fig. 3.2.3 to Fig. 3.27.

The effective address (EA) is used to access the first operand. The second operand is always contained in an internal CPU register with the result of the operation replaced in this same register. Note that the program counter (R7) is incremented before the Operation Code is performed; thus, if the destination register (DDD) specified by the instruction is R7, the incremented program counter is modified creating the effect of a branch in the program sequence.

#### DIRECT ADDRESS (Mode=000)

| PC   | Future Use | 1 | 0] | PC | ode | 0 | 0 | 0 | D | D | D |

|------|------------|---|----|----|-----|---|---|---|---|---|---|

| PC+1 | aaaaaa     | Α | A  | A  | Α   | A | A | A | A | A | A |

PC - PC + 2

EA aaaaaa AAAAAAAAAA

Note: aaaaaa is dependent upon the memory word size.

#### FIG. 3.2.3

INDIRECT ADDRESS (Mode=001 to 110)

| PC | Future Use              | 1   | OP Code  | M                       | M   | Μ            | D          | DI    | 2      |     |  |  |  |

|----|-------------------------|-----|----------|-------------------------|-----|--------------|------------|-------|--------|-----|--|--|--|

|    | MMM = 001,              | 01  | 0, 011   | MN                      | ИΜ  | = ]          | .00,       | 101   |        |     |  |  |  |

|    | $PC \rightarrow PC + 1$ |     |          | $PC \rightarrow PC + 1$ |     |              |            |       |        |     |  |  |  |

|    | EA-(MMM)                | )   |          | EA-(MMM)                |     |              |            |       |        |     |  |  |  |

|    |                         |     |          | <b>(</b> M              | IMN | /I)-         | <b>(</b> N | IMM   | i) + 1 | L   |  |  |  |

|    | MMM = 110 t             | for | MVO only | MN                      | ИM  | = 1          | 10 :       | for 1 | ion-   | MVO |  |  |  |

|    | PC - PC + 1             |     |          | PC                      |     | PC           | +1         |       |        |     |  |  |  |

|    | EA-(MMM)                | )   |          | <b>(</b> M)             | ΜN  | 1)-          | -(MI       | MM)   | 1      |     |  |  |  |

|    | (MMM) <del>-</del> (M   | MM  | 1) + 1   | EA                      | -   | - <b>(</b> M | IMN        | 1)    |        |     |  |  |  |

#### FIG. 3.2.4

## IMMEDIATE DATA (Mode=111)

| PC   | Future Use | 1 | OP | Co | de | 1    | 1   | 1 | D | D | D |

|------|------------|---|----|----|----|------|-----|---|---|---|---|

| PC+1 | iiiiii     | I | I  | Ι  | I  | I    | I   | I | I | I | I |

|      |            |   | ]  | ΕA |    | - PC | 2 + | 1 |   |   |   |

Note: i i i i i i i s dependent upon the memory word size.

FIG. 3.2.5

#### INDIRECT ADDRESSED DOUBLE BYTE DATA

| PC-1 | Future Use                     | 0  | 0 0 0   | 000                   | 001    | SDBD instruction |  |  |  |  |  |  |  |  |

|------|--------------------------------|----|---------|-----------------------|--------|------------------|--|--|--|--|--|--|--|--|

| PC   | Future Use                     | 1  | OP Code | МММ                   | DDD    |                  |  |  |  |  |  |  |  |  |

| 1    | PC - PC + 1                    |    |         |                       |        |                  |  |  |  |  |  |  |  |  |

|      | If MMM = 1, 2, 3 If MMM = 4, 5 |    |         |                       |        |                  |  |  |  |  |  |  |  |  |

|      | EA <sub>L</sub> -(MMM          | [) | E       | AL-(MN                | IM)    |                  |  |  |  |  |  |  |  |  |

|      | EA <sub>H</sub> ≁-(MMM         | [) | (N      | 1MM) <del>-</del> (1  | MMM) + | 1                |  |  |  |  |  |  |  |  |

|      |                                |    | E       | EA <sub>H</sub> (MMM) |        |                  |  |  |  |  |  |  |  |  |

|      |                                |    | (N      | IMM)                  | (MMM)  | + 1              |  |  |  |  |  |  |  |  |

Note: The SDBD instruction must immediately preceed the external reference instruction. Mode 000 and 110 are not supported for double byte data operations by this version of the CP-1600.

FIG. 3.2.6

IMMEDIATE DOUBLE BYTE DATA

| PC-1 | Future Use | 0  | 0  | 0  | 0  | 0 | 0 | 0 | 0 | 0 | 1 | SDBD instru |

|------|------------|----|----|----|----|---|---|---|---|---|---|-------------|

| PC   | Future Use | 1  | OP | Co | de | Ι | Ι | I | D | D | D |             |

| PC+1 | Not Used   |    |    | L  | L  | L | L | L | L | L | L |             |

| PC+2 | Not Used   |    |    | U  | U  | U | U | U | U | U | U |             |

|      | PCPC + 3   |    |    |    |    |   |   |   |   |   |   | '           |

|      | EAL-(PC+)  | 1) |    |    |    |   |   |   |   |   |   |             |

|      | EAH-(PC+2  | 2) |    |    |    |   |   |   |   |   |   |             |

Note: The assembler will automatically generate the SDBD instruction preceeding the external reference instruction when the constant specified by the assembly language statement exceeds the memory word size specified. If the user specifies the SDBD, then the data word will always be generated to fill two bytes.

# FIG. 3.2.7

uction

# 3.3 INTERNAL REFERENCE INSTRUCTIONS

The Internal Reference instructions, which has a zero in the high order bit position of the Operation Field, process data already held within the 8 working registers of the CP-1600. These instructions are grouped into register to register, register shift, single register, and internal control instructions. The basic formats are depicted in Fig. 3.3.1 to Fig. 3.3.5.

## 3.3.1 REGISTER TO REGISTER

| 15 10      | 9 | 8 7 6   | 5 4 | 3 | 2 1 | 0 |

|------------|---|---------|-----|---|-----|---|

| Future Use | 0 | OP Code | S S | S | DD  | D |

#### OPERATION

| (010) | MOVe Register         | (MOVR) |

|-------|-----------------------|--------|

| (011) | ADD Register          | (ADDR) |

| (100) | SUBtract Register     | (SUBR) |

| (101) | CoMPare Register      | (CMPR) |

| (110) | logical AND Register  | (ANDR) |

| (111) | eXclusive OR Register | (XORR) |

## FIG. 3.3.1

# 3.3.2 REGISTER SHIFT

| 15 10      | 9 | 8 | 7 | 6 | 5 | 4 | 3 | 2 | 1 | 0 |

|------------|---|---|---|---|---|---|---|---|---|---|

| Future Use | 0 | 0 | 0 | 1 | В | L | A | N | D | D |

#### MODE

| B=1, | Right Shift      | B=0, | Left Shift        |

|------|------------------|------|-------------------|

| L=1, | With Link Bits   | L=0, | No Link Bits      |

| A=1, | Arithmetic       | A=0, | Logical or Rotate |

| N=1, | 2 Position Shift | N=0, | 1 Position Shift  |

|      |                  |      |                   |

Note: Shifts can only be performed on Registers R0 - R3.

FIG. 3.3.2

# 3.3.3 SINGLE REGISTER

| 15 10      | 9 | 8 | 7 | 6 | 5  | 4    | 3   | 2 | 1 | 0 |

|------------|---|---|---|---|----|------|-----|---|---|---|

| Future Use | 0 | 0 | 0 | 0 | OF | ° Co | ode | D | D | D |

## OPERATION

| 001 | INCrement Register               | (INCR) |

|-----|----------------------------------|--------|

| 010 | DECrement Register               | (DECR) |

| 011 | COMplement Register              | (COMR) |

| 100 | NEGate (2's complement) Register | (NEGR) |

| 101 | ADd Carry bit Register           | (ADCR) |

| 110 | Get Status WorD register *       | (GSWD) |

| 111 | Restore Status WorD register     | (RSWD) |

## FIG. 3.3.3

### 3.3.4 INTERNAL CONTROL

| 15 10      | 9 | 8 | 7 | 6 | 5 | 4 | 3 | 2  | 1    | 0   |

|------------|---|---|---|---|---|---|---|----|------|-----|

| Future Use | 0 | 0 | 0 | 0 | 0 | 0 | 0 | OF | ° Co | ode |

#### OPERATION

| 000 | HaLT                          | (HLT)  |

|-----|-------------------------------|--------|

| 001 | Set Double Byte D <b>at</b> a | (SDBD) |

| 010 | Enable Interrupt System       | (EIS)  |

| 011 | Disable Interrupt System      | (DIS)  |

| 101 | Terminate Current Interrupt   | (TCI)  |

| 110 | CLeaR Carry Bit               | (CLRC) |

| 111 | SET Carry Bit                 | (SETC) |

## FIG. 3. 3.4

\* The GSWD instruction can use only R0, R1, R2, or R3 as register specifications for true Get Status Word operation. Use of R4 or R5 results in a NOP instruction. Use of R6 or R7 results in a NOP internal to the CP-1600 and causes a pulse to be outputted on the PCIT\* pin. This can be used to cause an interrupt to form a Software Interrupt (SIN) or Trap instruction.

#### 3.3.5 JUMP/JUMP AND SAVE RETURN

| PC   | Future Use | 0 | 0 | 0 | 0 | 0 | 0 | 0          | 1 | 0 | 0 |

|------|------------|---|---|---|---|---|---|------------|---|---|---|

| PC+1 | Future Use | В | В | A | A | A | A | A          | A | D | Е |

| PC+2 | Not Used   | A | A | A | A | A | A | <b>A</b> . | A | A | A |

| DC12 |            |   |   |   |   |   |   |            |   |   |   |

PC+3

#### FIG. 3.3.5

The instructions in the jump group occupy three consecutive memory locations and are used to perform direct jumps and subroutine calls. In addition the interrupt system can be either enabled or disabled by bits 0-1 of the second word of the instruction.

On direct jumps the return address is not saved. The destination address is formed by using bits 2-7 of the second word as bits 10-15 of the jump address and using bits 0-9 of the third word as bits 0-9 of the jump address.

On subroutine jumps, the return address (PC+3) is saved in register 4, 5, or 6. This register designation is formed by using bits 8-9 of the second word (field BB) and adding 4. Note if BB=3, the designated register becomes 7 (the PC) which is the jump instruction. By using one of the Jump and Save instructions, the linkage to a subroutine is accomplished with the return address saved in register 1BB.

## INSTRUCTION SET

#### **REGISTER - REGISTER**

| S, DDD<br>S<br>S<br>S, DDD<br>S, DDD<br>S, DDD | 6 *<br>6 *<br>7<br>6<br>6                                                                   | 0010<br>0010<br>0010<br>0011                         | SSS<br>SSS<br>SSS                                                                                                                                                                                                                                                                                                                         | DDD<br>SSS                                                                                                                                                                                                                                                                                                                                                                                                               | MOVe contents of Register SSS to register DDD. *If DDD is 6 or 7 add 1 to Cycles.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | S, Z                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

|------------------------------------------------|---------------------------------------------------------------------------------------------|------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| S<br>S, DDD<br>S, DDD<br>S, DDD                | 7<br>6                                                                                      | 0010<br>0010                                         | SSS                                                                                                                                                                                                                                                                                                                                       |                                                                                                                                                                                                                                                                                                                                                                                                                          |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

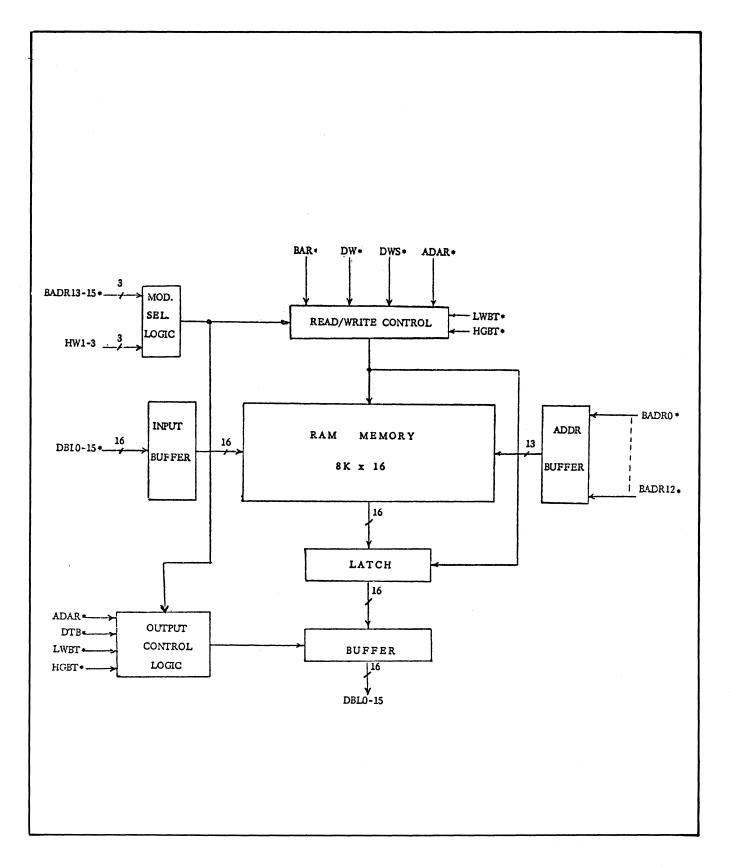

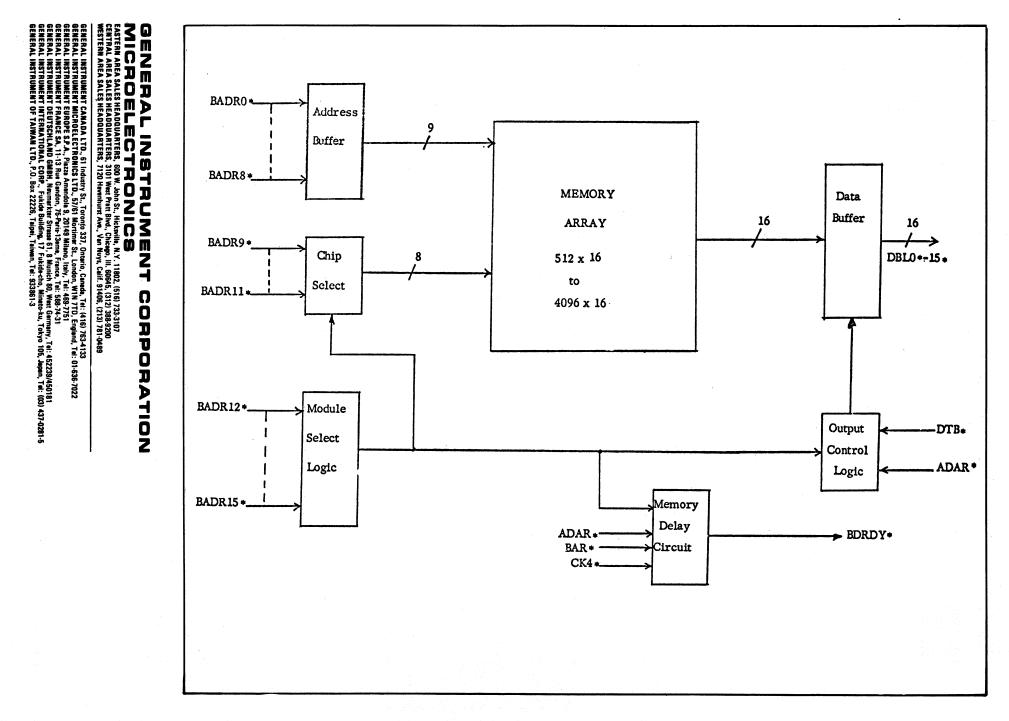

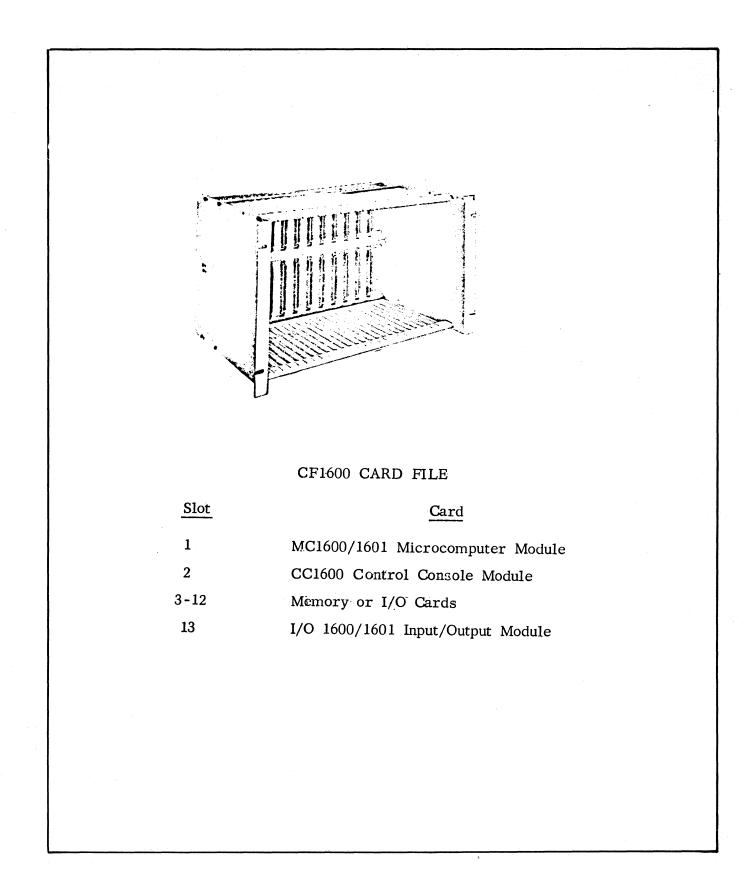

| S, DDD<br>S, DDD<br>S, DDD                     | 6                                                                                           |                                                      | CCC                                                                                                                                                                                                                                                                                                                                       |                                                                                                                                                                                                                                                                                                                                                                                                                          | TeST contents of Register SSS. *If SSS is 6 or 7 add 1 to Cycles.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | S, Z                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |